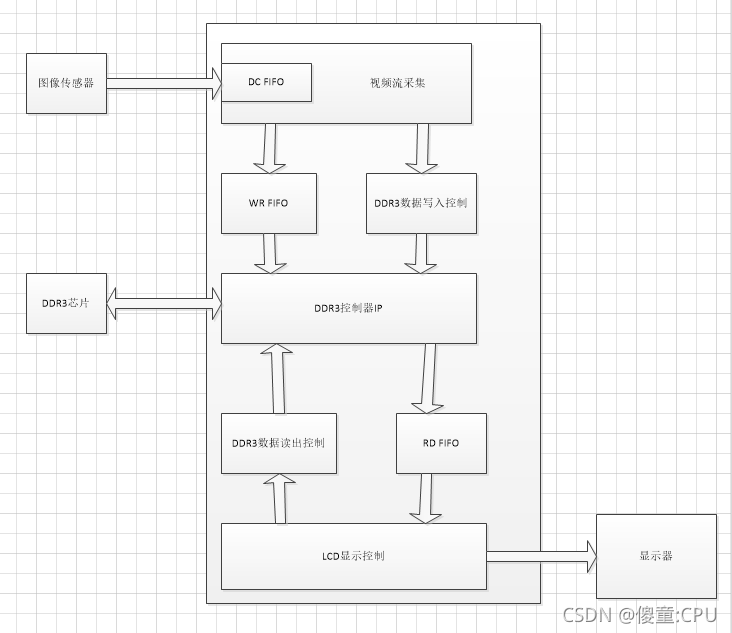

灰度图像采集显示

在FPGA内部,采集到的视频数据线通过一个FIFO,将原本与25MHZ时钟同步的数据流转换到FPGA内部50MHZ的时钟。接着将这个数据再送入写DDR3缓存的异步FIFO中,这个FIFO中的数据一旦达到一定数量,就会被写入DDR3中。于此同时,使用另一异步FIFO缓存从DDR3读出的图像数据;LCD驱动模块不断地发出读图像数据请求给到这个FIFO,从中读取图像数据并送给VGA显示器进行实时图像的显示。

视频流采集设计

在传感器上电并且输入时钟信号后,同步信号和数据总线便开始配合输出视频数据流。上图是传感器输出VGA(752x480像素)并行数据视频流协议的时序波形。场同步信号FRAME_VALID的每一个高脉冲表示新的一场图像(或者说是新的一帧图像)正在传输;行同步信号LINE_VALID为高电平时,表示目前的数据总线DOUT[9:0] (实际只是用高8位)上的数据是有效的的视频流。FRAME_VALID拉高后开始,在LINE_VALID为高电平期间依次传输的是第一行 、第二行、第三行、。。。。、第四百八十行数据,每一行包含了752像素的灰

)

)