概括

本应用说明介绍了使用AMD Vivado™ 设计套件生成加密比特流和加密密钥(高级加密标准伽罗瓦/计数器模式 (AES-GCM) 和 RSA 身份验证)的简单分步过程。其中还介绍了使用Vivado 设计套件将高级加密标准全球移动通信系统 (AES-GSM) 加密密钥和 RSA 公钥哈希值以及加密比特流编程到AMD UltraScale™ FPGA中的步骤。本应用说明适用于AMD UltraScale™ 和AMD UltraScale+™ FPGA。本文档不旨在讨论安全问题,例如生成密钥或选择初始化向量 (IV) 以符合美国国家标准与技术研究院 (NIST) 标准。

介绍

UltraScale器件具有片上 AES-GCM 解密和身份验证逻辑,可提供高度的设计安全性。加密的UltraScale FPGA 设计无法复制或进行逆向工程。UltraScale FPGA AES 系统包含基于软件的比特流加密和片上比特流解密,并配有专用存储器用于存储加密密钥和加密比特流。加密密钥和加密比特流均使用Vivado工具生成 。

UltraScale器件将加密密钥内部存储在专用 RAM(由小型外部连接电池备份,称为电池备份 RAM (BBRAM))或 eFUSE 中。如果使用 RSA 身份验证,则必须将 RSA 公钥的哈希值编程到 eFUSE 中。加密密钥只能通过 JTAG 端口编程到器件中。BBRAM 和 eFUSE 均无法读回。在配置期间,UltraScale 器件执行反向操作,解密传入的比特流。UltraScale FPGA AES 加密逻辑使用 256 位加密密钥。片上 AES 解密逻辑不能用于比特流解密以外的任何用途;例如,AES 解密逻辑不可用于用户设计,也不能用于解密配置比特流以外的任何数据。

高级加密标准和身份验证

UltraScale FPGA 加密系统采用 AES-GCM 认证加密算法。AES 是 NIST 和美国商务部支持的官方标准(有关更多信息,请参阅高级加密标准 (AES) ( FIPS PUB 197 ) 和 GCM 规范Galois/计数器操作模式 (GCM)(规范))。

AES-GCM 的优势在于它还支持内置身份验证。UltraScale FPGA AES 加密系统使用 256 位加密密钥(NIST 描述的 128 位和 192 位备用密钥长度未实现)来一次加密或解密 128 位数据块。根据 NIST 的说法,256 位密钥有 1.1 x 10 77 种可能的密钥组合。为了获得最安全的方法,建议您手动创建此 256 位密钥,而不是使用Vivado提供的伪随机密钥生成器功能。

比特流认证

AES-GCM 加密标准支持内置身份验证,从而增强了安全性,无需像7 系列FPGA 那样指定单独的 HMAC 密钥。如果不知道 AES-GCM 密钥,比特流就无法被修改或伪造。加密提供了基本的设计安全性,以防止设计被复制或逆向工程,而身份验证则确保用于 FPGA 配置的比特流是由授权用户创建的未经修改的比特流。身份验证可以验证比特流的数据完整性和真实性。

身份验证涵盖所有类型控制和数据的整个比特流。任何比特流篡改(包括单个比特翻转)都会被检测到。如果身份验证通过,配置将在启动周期内完成。如果身份验证失败,且 AES-GCM 引擎检测到任何比特流更改,设备将无法启动。如果启用了回退功能,则在清除整个设备配置后加载回退比特流。如果未启用回退功能,则配置逻辑将禁用配置接口,阻止任何对 FPGA 的访问。需要发送 PROGRAM_B 信号脉冲或上电复位才能复位配置接口。您需要选择以下两种比特流身份验证方式之一:

- 如果您使用比特流加密,则可以依赖 AES-GCM 标准内置的身份验证。

- 此外,您可以依赖 RSA-2048 身份验证在解密比特流之前对其进行身份验证。以下段落将讨论 RSA-2048。

RSA 身份验证

AES-GCM 是一种使用对称密钥的自认证算法,这意味着加密密钥与解密密钥相同。由于此密钥是秘密的(因此存储在内部密钥空间中),因此必须加以保护。UltraScale架构提供了一种替代的身份验证形式,即 RSA-2048。RSA 是一种非对称算法,这意味着验证密钥与签名密钥不同。验证使用公钥完成。此公钥无需保护,也无需特殊的安全存储。如果需要,这种身份验证形式可以与加密结合使用,以同时提供真实性和机密性。RSA 不仅具有使用公钥的优势,还具有先认证后解密的优势。RSA 公钥的哈希值必须存储在 eFUSE 中。

UltraScale FPGA 支持 RSA-2048 算法,用于在比特流数据发送到解密器之前对其进行身份验证。此方法可在执行任何解密操作之前确保数据真实可靠,从而有助于防止对解密引擎本身的攻击。RSA 配置控制逻辑将加密的比特流(包括公钥和比特流签名)读入器件存储器。然后,RSA 配置控制逻辑指示 RSA 引擎根据公钥和签名计算预期摘要。

比特流缓冲后,RSA 引擎计算出预期摘要,然后将实际摘要与结果进行比较。如果 RSA 认证通过且配置数据已加密,则释放 FPGA 以解密比特流。如果 RSA 认证失败,则会生成与 AES-GCM 认证错误相同的错误。此时,设备要么锁定,要么(如果启用)执行回退操作。

配置了 RSA 认证比特流的设备所需的时间最多是配置标准未压缩比特流的三倍。实际时间取决于配置模式。RSA 认证不能与比特流压缩、部分重配置或通过 PCIe® 接口(包括串联解决方案)的配置一起使用。

特定配置模式和位宽的UltraScale和UltraScale+器件支持 RSA 身份验证。有关支持 RSA 身份验证的 UltraScale FPGA 器件和配置模式,请参阅《UltraScale 架构配置用户指南》 ( UG570 )中的“RSA 身份验证”部分。

按键滚动

UltraScale FPGA 允许您将比特流分解为多个 AES 加密消息,每个消息都使用其自己唯一的密钥进行加密。此功能称为滚动密钥,初始密钥存储在芯片上,而每个连续消息的密钥都在前一个消息中加密(包装)。滚动密钥提高了对差分功率分析 (DPA) 等侧信道攻击的安全性。比特流选项 BITSTREAM.ENCRYPTION.KEYLIFE 定义每个密钥的加密块数量。每个密钥的加密块越少,安全性就越高,但会大大增加比特流大小,从而增加配置时间。选择 1,024 或更高的值会使配置大小增加约 15%,选择 64 的值会使比特流大小增加 50%,选择 32(默认值)会使比特流大小增加一倍以上。下图显示了比特流大小乘数与每个密钥的块数的关系。

加密比特流实现概述

- 选择 AES 密钥存储位置:BBRAM 或 eFUSE;以及相应的安全选项。(请参阅《使用UltraScale 和 UltraScale+ FPGA 开发防篡改设计》 ( XAPP1098 ),了解 BBRAM 和 eFUSE 之间的权衡)。

- 选择是否使用 RSA 身份验证:启用 AES-GCM 或 AES-GCM 和 RSA 身份验证。(请参阅《使用 UltraScale 和 UltraScale+ FPGA 开发防篡改设计》 ( XAPP1098 ),了解 AES-GCM 和 RSA 身份验证之间的权衡)。

- 根据您选择的 AES 密钥存储位置在电路板设计中实现硬件要求。

- 使用Vivado Design Suite软件,生成 AES 密钥或向软件提供您自己的自定义 AES 密钥(这始终是最安全的方法)并加密比特流:

- 生成/创建 AES 密钥。

- 如果选择 RSA 作为身份验证方法,请使用 OpenSSL ( www.openssl.org ) 或其他密钥生成软件生成 RSA 公钥/私钥对。

- 使用 JTAG 接口将 AES 密钥编程到 FPGA 中。

- 通过JTAG或其他配置模式(如SPI或BPI)将加密的位文件编程到FPGA中。 注意:对于支持 RSA 身份验证的UltraScale FPGA 设备和配置模式,请参阅UltraScale 架构配置用户指南( UG570 )中的 RSA 身份验证部分。

- 执行硬件验证以确保正常运行。

硬件板要求

实现加密设计流程有一些基本的硬件要求:

- 对于编程能力和调试能力:与 FPGA 的 JTAG 连接。

-

对于 BBRAM 密钥存储:电池连接至 V BATT(有关电池电压,请参阅相应的数据表

要求)。

-

对于 eFUSE 密钥存储:建议使用 V BATT或 V CCAUX来启用测试功能

烧录一次性可编程 (OTP) eFUSE 之前的 BBRAM 流程。

软件要求

建议使用Vivado Design Suite 2017.1 或更新版本。

AES 密钥存储

考虑 AES-GCM 密钥存储时有两个选项:BBRAM 或 eFUSE。

以下各节详细介绍了它们各自的优缺点。有关每种存储选项的更多信息,请参阅《UltraScale 架构配置用户指南》 ( UG570 )。

BBRAM存储位置

当加密密钥存储在 FPGA 的电池供电 RAM 中时,加密密钥存储单元属于易失性数据,必须持续供电才能保留其内容。正常工作期间,这些存储单元由辅助电压输入 (V CCAUX ) 供电。

下表列出了 BBRAM 存储位置的优点和缺点。

| 优势 | 缺点 |

|---|---|

|

|

| |

eFUSE 是一种非易失性一次性可编程技术,用于特定配置设置。通过特定时间的大电流来编程(或烧断)保险丝链。用户可编程 eFUSE 可以使用AMD配置工具进行编程。

例如,如果某个寄存器的访问被禁用,则无法重新启用。FPGA 逻辑只能访问 FUSE_USER 寄存器的值。所有其他 eFUSE 位均无法从 FPGA 逻辑访问。下表列出了 eFUSE 存储位置的优缺点。

| 优势 | 缺点 |

|---|---|

|

|

混淆密钥

UltraScale FPGA 支持您将 AES 密钥以混淆格式加载到器件中。这样,您就可以将混淆后的密钥提供给合同制造商,而无需向其公开真正的 AES-256 密钥。设置 BITSTREAM.ENCRYPTION.OBFUSCATEKEY 属性后,Vivado write_bitstream 软件会在输出 NKY 文件中创建一个新密钥 ObfuscateKey。此混淆密钥是通过使用存储在硅片中的金属化系列密钥加密您的 AES-256 密钥而创建的。所有UltraScale器件和所有UltraScale+ FPGA 都使用相同的密钥。(UltraScale FPGA 系列密钥与UltraScale+ FPGA 系列密钥不同。)

AMD不提供Vivado工具系列密钥。客户必须将系列密钥请求发送至 secure.solutions@xilinx.com。之后,我们将通过www.amd.com上的产品许可网站将系列密钥分发给符合条件的客户。

BITSTREAM.ENCRYPTION.FAMILY_KEY_FILEPATH C:/<any directory>/familyKey_us.cfg [current_design]

您可以将加密密钥(而非实际的 AES-256 密钥)提供给合同制造商。当密钥被编程到 eFUSE 或 BBRAM 中时,如果 NKY 文件包含某个KeyObfuscate字段,则存储位置会自动设置一个标志,指示此密钥已加密。生成的比特流还包含附加指令,用于通知芯片在使用密钥解密比特流的其余部分之前,先解密相应的 AES-256 密钥存储位置。比特流所选位置的加密密钥设置必须与比特流的加密密钥设置匹配。BITSTREAM.ENCRYPTION.OBFUSCATEKEY 属性与 BBRAM 密钥存储的配置计数 DPA 对策不兼容。

eFUSE寄存器

UltraScale FPGA 总共有六个 eFUSE 寄存器:FUSE_RSA、FUSE_KEY、FUSE_DNA、FUSE_USER、FUSE_CNTL 和 FUSE_SEC。本应用笔记的重点不在于 FUSE_DNA 寄存器。下表列出了所有 UltraScale eFUSE寄存器。

| 注册名称 | 大小(位) | 内容 | 描述 |

|---|---|---|---|

| FUSE_RSA | 384 | 比特流认证密钥 [383:0] (首先移位 0 位) | 存储用于 RSA 比特流认证的公钥的哈希值。 |

| 保险丝钥匙 | 256 | 比特流加密密钥 [255:0] (首先移位 0 位) | 存储用于 AES-GCM 比特流解密和身份验证的密钥。可以使用 eFUSE 密钥代替存储在电池供电 SRAM (BBRAM) 中的密钥。UltraScale FPGA 解密引擎使用 AES 密钥加载加密比特流。根据 CNTL 寄存器中的读/写访问位,AES 密钥可以通过 JTAG 端口进行编程,但不能通过 JTAG 端口读取。 |

| FUSE_DNA | 96 | 由AMD编程的设备标识符 [95:0] (首先移位 0 位) | 唯一设备标识符位 [95:0],对应 96 位只读 DNA_PORTE2 原始值,称为设备 DNA。 |

| FUSE_用户 | 32 或 128 | 用户定义 [31:0] 或 [127:0] (首先移位 0 位) | 存储 32 位或 128 位用户定义代码。该寄存器的 32 位版本可使用 eFUSE_USR 原语从 FPGA 逻辑读取。(有关 eFUSE_USR 原语的描述,请参阅《UltraScale架构配置用户指南》(UG570) [参照 3] 第 7 章“设计输入”)。根据 CNTL 寄存器中的读/写访问位,可以通过 JTAG 端口对代码进行编程和读取。 该寄存器的 128 位版本存储 128 位用户定义代码。该寄存器可通过 JTAG FUSE_USER_128 指令读取。JTAG FUSE_USER_128 数据寄存器的长度在UltraScale FPGA 中为 384 位,在UltraScale+ FPGA中为 176 位 。仅支持 [127:0] 位用于存储用户代码,其余位保留,可以为任意值。 |

| 保险丝控制 | 21 | 控制位 CNTL [20:0] (首先移位 0 位) | 控制密钥使用以及对 eFUSE 寄存器的读/写访问。该寄存器可通过 JTAG 端口进行编程和读取。 |

| 24 | 控制位 CNTL [23:0] (首先移位 0 位) | 在UltraScale+ FPGA 中,这些位控制密钥的使用以及对 eFUSE 寄存器的读/写访问。该寄存器可以通过 JTAG 端口进行编程和读取。 | |

| FUSE_SEC | 32 | 安全控制位 [31:0] (首先移位 0 位) | 控制加密和身份验证选项。根据 CNTL 寄存器中的读/写访问位,该寄存器可以通过 JTAG 端口进行编程和读取。 |

eFUSE 控制寄存器 (FUSE_CNTL) 位描述

该寄存器包含用户可编程位,用于选择 AES 密钥的使用方式以及设置其他 eFUSE 寄存器的读/写保护。下表提供了位说明和推荐设置。

| 少量 | 位名称 | 描述 | 推荐设置 |

|---|---|---|---|

| 0 | R_DIS_Key | 当编程为 1 时,该位将禁用验证 AES 密钥和 AES 密钥编程的 CRC 校验。 | 是(编程为 1) |

| 1 | R_DIS_USER | 该位设置为 1 时,将禁用读取 FUSE_USER 用户代码。这不会禁用通过 EFUSE_USR 组件读取用户代码,但会禁用通过 JTAG 端口读取用户代码。 | 不 (保持为 0) |

| 2 | R_DIS_SEC | 当编程为 1 时,该位禁用通过 JTAG 读取 FUSE_SEC 安全设置。 | 是(编程为 1) |

| 3–4 | 保留 | 保留 | – |

| 5 | 工作指示 | 当编程为 1 时,该位将禁用 FUSE_CNTL 位的编程。 建议:在编程 FUSE_CNTL 寄存器位后将此位编程为 1,以防止对 FUSE_CNTL eFUSE 位进行意外更改。 | 是(编程为 1) |

| 6 | R_DIS_RSA | 当编程为 1 时,该位禁用读取 FUSE_RSA 认证密钥。 | 是(编程为 1) |

| 7 | 写入磁盘密钥 | 当编程为 1 时,该位将禁用 AES 密钥的编程和验证密钥的 CRC 校验。 建议:在编程密钥后对此位进行编程,以防止对 eFUSE AES 密钥值进行意外更改/损坏。 | 是(编程为 1) |

| 8 | W_DIS_USER | 禁用 FUSE_USER 用户代码的编程。 | 不 (保持为 0) |

| 9 | 工作区 | 当编程为 1 时,该位将禁用 FUSE_SEC 寄存器位的编程。 建议:在对 FUSE_SEC 寄存器进行编程后对此位进行编程,以防止对 FUSE_SEC 寄存器进行意外更改/损坏。 | 是(编程为 1) |

| 10–14 | 保留 | 保留 | – |

| 15 | W_DIS_RSA | 当编程为 1 时,该位禁用 FUSE_RSA 认证密钥的编程。 | 待处理的客户安全要求 |

| 16 | W_DIS_USER_128 | 当编程为 1 时,该位禁用 FUSE_USER_128 用户代码的编程。 | – |

| 17–23 | 保留 | 保留的UltraScale位延伸至位 20,保留的UltraScale+位延伸至位 23。 | – |

eFUSE 安全寄存器 (FUSE_SEC) 描述

该寄存器包含用户可编程位,用于选择 eFUSE 安全设置并启用 RSA 身份验证(如果需要)。下表提供了位说明和推荐设置。

| 少量 | 位名称 | 描述 | 推荐设置 |

|---|---|---|---|

| 0 | FUSE_SHAD_SEC[0] (CFG_AES_Only) | 仅允许加密的比特流。 如果此位被编程为 1,则除非已知 AES 密钥,否则无法使用器件。如果此位被编程,则无法接受退货授权 (RMA) 退货,并且无法使用Vivado间接 SPI/BPI 闪存编程流程。如果您打算使用Vivado进行此类编程,则必须在熔断此保险丝之前对外部配置存储器进行编程。 | 否(保持为 0) 建议:保留 0 个待处理的客户安全要求。 |

| 1 | FUSE_SHAD_SEC[1] | 强制使用存储在 eFUSE 中的 AES 密钥(BBRAM 密钥已禁用)。当此位未编程时,可以通过比特流选项选择加密和密钥源——FPGA 可以配置为使用未加密的比特流,或使用存储在电池供电 RAM (BBRAM) 或 eFUSE 中的密钥值加密的比特流。 | 否(保持为 0) |

| 2 | RSA 身份验证 | 强制 RSA 身份验证。 如果此位被编程为 1,则除非已知 RSA 密钥,否则无法使用器件。如果此位被编程,则无法接受退货授权 (RMA) 退货,并且无法使用Vivado间接 SPI/BPI 闪存编程流程。如果您打算使用Vivado进行此类编程,则必须在熔断此保险丝之前对外部配置存储器进行编程。 | 待处理的客户安全要求 |

| 4 | 扫描禁用 | 禁用AMD测试访问。 | 否(保持为 0) |

| 5 | CRYPT_DISABLE | 永久禁用解密器。 | 否(保持为 0) |

| 6 | FUSE_BKS_ENABLE | 启用密钥混淆。 | 由Vivado Design Suite自动设置 |

| 7–31 | 保留 | 保留 | - |

- 当 FUSE_SHAD_SEC[0:1] 未被编程时:

- 可以通过比特流选项启用或禁用加密。

- 可以通过比特流选项选择存储在 eFUSE 或电池支持的 SRAM (BBRAM) 中的 AES 密钥。

- 当 FUSE_SHAD_SEC[1:0] 被编程时。

- 只有使用 eFUSE 密钥加密的比特流才能用于通过外部配置端口配置 FPGA。

创建加密密钥和加密比特流

Vivado工具提供的比特流生成器 (write_bitstream)可以生成加密和非加密比特流。对于 AES 比特流加密,请设置 write_bitstream 属性以启用比特流加密。您可以指定一个自定义的 256 位密钥作为比特流生成器的输入(这是AMD 的建议,也是最安全的方法),或者您也可以让Vivado工具为您生成一个伪随机密钥(不推荐)。

对于 3D IC 器件,您必须为每个 SLR 分配一个包含唯一密钥的 NKY 文件。当您尝试为所有 SLR 分配单个 AES 密钥或为所有 SLR 分配单个 AES/IV 对时, Vivado硬件管理器会发出严重警告。这两种情况都会引入安全漏洞。

有关使用唯一加密密钥集的重要更新,请参阅答复记录71558、答复记录000036543和答复记录000033700。请参阅下方#vtx1717106533372__codeblock_dvz_gfb_qbc中的 3D IC NKY 文件示例。

比特流生成器会生成一个加密的比特流文件 (.BIT) 和一个加密密钥文件 (.NKY)。下表列出了可在 XDC 文件中定义的 write_bitstream 属性及其相应的描述。有关Vivado集成设计环境 (IDE) 中密钥创建和比特流加密的示例,请参阅《 Vivado 设计套件用户指南:编程和调试》 ( UG908 )。

| Write_bitstream 属性 | 默认值 | 可能的值 | 描述 |

|---|---|---|---|

| 比特流.加密.加密 | 不 | 否或是 | 加密比特流。 |

| 比特流.加密.加密密钥选择 | 布拉姆 | bbram 或 eFUSE | 确定要使用的 AES 加密密钥的位置,可以是电池供电的 RAM (BBRAM) 或 eFUSE 寄存器。 注意:仅当 加密选项设置为 True时,此属性才可用。 |

| 比特流.加密.密钥寿命 | 三十二 | 4至2,147,483,647 | 指定 AES-GCM 认证比特流中应使用单个密钥的 128 位加密块的数量。默认值为 32,会使比特流大小或比特流长度增加约 2 倍。当 BITSTREAM.AUTHENTICATION. AUTHENTICATE = 否时使用 |

| 比特流.加密.密钥0 | 挑选 | 选择或<256 位十六进制字符串> | Key0 设置比特流加密的 AES 加密密钥。要使用此选项,必须先将“加密”设置为“是”。 |

| 比特流.加密.密钥文件 | 没有任何 | <字符串> | 指定输入加密文件的名称(文件扩展名为 .nky)。要使用此选项,必须先将“加密”设置为“是”。 |

| 比特流.加密.RSAKEYLIFEFRAMES | 8 | 8至2,147,483,647 | 指定在指定 RSA 公钥认证的情况下,任何给定的 AES-256 密钥应使用多少个配置帧。8 个配置帧的值相当于使用 246 个加密块的密钥。当 BITSTREAM.AUTHENTICATION 设置为“是”时使用。AUTHENTICATE 设置为“是” |

| 比特流.加密.启动IV0 | 挑选 | 选择或<128 位十六进制字符串> | 用于指定第一条 AES-GCM 消息中初始 GCM 计数值的初始化向量。128 位十六进制值。仅使用 128 个十六进制值的前 96 位。后 32 位将被丢弃。 |

| 比特流加密启动混淆 | 挑选 | 选择或<128 位十六进制字符串> | 起始混淆初始向量(混淆 IV0)值。仅使用 128 个十六进制值的前 96 位。后 32 位将被丢弃。 |

| 比特流.身份验证.身份验证 | 不 | 是还是不是 | 指示是否使用 RSA 身份验证。如果否,则使用 AES-GCM 固有的身份验证。 |

| BITSTREAM.AUTHENTICATION.RSAPRIVATEKEYFILE | 没有任何 | <字符串> | 指定包含用于签署 RSA-2048 认证比特流的密钥对的 OpenSSL .pem 文件。 |

| 比特流加密混淆密钥 | 禁用 | 启用或禁用 | 创建比特流,用于加密比特流的密钥在写入 eFUSE 或电池供电 RAM (BBRAM) 之前会进行混淆处理。这允许用户向设备编程器提供混淆密钥,而非原始客户密钥。然后,设备编程器可以将混淆密钥写入 eFUSE 或 BBRAM,并使用所选存储位置中的混淆密钥标记将其标记为已混淆。 |

以下特定的 XDC 文件代码片段展示了 BBRAM 密钥存储和定义的自定义密钥。如果您希望工具生成伪随机密钥,则需要注释掉该BITSTREAM.ENCRYPTION.KEY0属性。这还显示已启用 RSA 身份验证,并将 RSA 密钥有效期设置为默认值 8。注释掉这些内容即可禁用 RSA 身份验证功能。所有显示的属性也可通过“编辑设备属性” GUI 进行选择和编辑。

#Encryption settings

set_property BITSTREAM.ENCRYPTION.ENCRYPT YES [current_design]

#set_property BITSTREAM.ENCRYPTION.ENCRYPTKEYSELECT EFUSE [current_design] set_property BITSTREAM.ENCRYPTION.ENCRYPTKEYSELECT BBRAM [current_design]

set_property BITSTREAM.ENCRYPTION.OBFUSCATEKEY Enable [current_design]

set_property BITSTREAM.ENCRYPTION.KEYLIFE 32 [current_design]

set_property BITSTREAM.ENCRYPTION.KEY0 256'h1234567812345678123456781234567812345678123456781234567812345678 [current_design] set_property BITSTREAM.ENCRYPTION.STARTIV0 128'h87654321876543218765432187654321 [current_design]

set_property BITSTREAM.ENCRYPTION.STARTIVOBFUSCATE 128'hABCDABCDABCDABCDABCDABCDABCDABCD[current_design]

set_property BITSTREAM.ENCRYPTION.FAMILY_KEY_FILEPATH

C:/<any directory>/familyKey_us.cfg [current_design] #Authentication settings

set_property BITSTREAM.AUTHENTICATION.AUTHENTICATE YES [current_design]

set_property BITSTREAM.ENCRYPTION.RSAKEYLIFEFRAMES 8 [current_design]

set_property BITSTREAM.AUTHENTICATION.RSAPRIVATEKEYFILE {C:config/ultrascale/encryption/encryption_test/encryption_test.runs/impl_1/rsa.pem} [current_design]

NKY 文件生成与比特流生成同时进行。此文件采用与比特文件相同的顶级名称,并与加密比特流位于同一实现目录中。单片设备的 NKY 文件格式为:

Device <type>;

EncryptKeySelect <type>;

StartIvObfuscate 00000000000000000000000000000000;

RsaPublicKeyDigest 000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000;

Key0 0000000000000000000000000000000000000000000000000000000000000000;

StartIV0 00000000000000000000000000000000;

对于 3D IC 设备,NKY 文件格式Key和StartIV语句扩展了第二个值,指示目标 SLR 指数。

Device <type>;

EncryptKeySelect <type>;

StartIvObfuscate 00000000000000000000000000000000;

RsaPublicKeyDigest 000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000;

Key0 0000000000000000000000000000000000000000000000000000000000000000, 0;

StartIV0 00000000000000000000000000000000, 0;

Key0 0000000000000000000000000000000000000000000000000000000000000000, 1;

StartIV0 00000000000000000000000000000000, 1;

| 范围 | 向量大小(十六进制) |

|---|---|

| 启动IVObfuscate | 128小时 |

| RsaPublicKeyDigest | 384'小时 |

| 键0 | 256'小时 |

| 启动IV0 | 32'小时 |

例如:(top.nky,单片设备)

Device xcvu095;

EncryptKeySelect BBRAM;

StartIvObfuscate abcdabcdabcdabcdabcdabcdabcdabcd;

RsaPublicKeyDigest 6DF61AA1636F1FF8A35D064CED96918A6D4820D3CAEEFFA47F64F5C58AC2E539CA3A53103C86450EC576AD595AB3A528;

Key0 1234567812345678123456781234567812345678123456781234567812345678;

StartIV0 876543218765432187654321000003f8;

Key1 44a619e399910767e68cb81bcbae831bd5d10a96e5a348420e9384eb0df06111;

StartIV1 b152ef23b9481138af45a21a000003d8;

.

.

.

Key4063 ddd9955fae4847a54d10a1c06a52171cf69e3593220018c2cac4ca56bf359f5c;

StartIV4063 7d94e42bf79ab77cce1a1d8300000382;

RSA 认证 PEM 文件,示例语法:

-----BEGIN RSA PRIVATE KEY----- MIIEpQIBAAKCAQEAvCMmT6/MM9LxXs7ZxybE4wKACvp0S2EpWy/q+wFkjeev/oT1EZkyRkeCLWKwLaTUeGxFYeWCVFhpHH7PU9d/5HudIsV

r/uJ8k/V7GASsj/8EL3O+RFoMdpsv6AFFD8desse3svR2d3yWlnrWLKfSd25DLqOg5fHMauV5DwDpsrbUvBf/ZOW5JWd4iyi0oeK1/Dw/91

AYiJoRWmKt6s3IH1ZkX4OfoXMBJ+SnVgV9NIm59lOb0vd0ZZtNOqo1oX/Ekn93jwoD1UbHAWN90TfZSIAqsv2c4aeC342jKrHUq4cykK

.

.

.

xuTbhBadZaq8u8TGsXO3oPvI+p2tee5sNNoleJj3/gnkPtF9od5bqo8=

-----END RSA PRIVATE KEY-----

加载加密密钥

BBRAM 和 eFUSE 256 位对称密钥只能使用Vivado设备编程器工具通过 JTAG 接口加载到设备上。对于UltraScale设备,此密钥加载路径对设备而言是只写的。没有物理数据路径可以读回任何密钥。当通过 JTAG 将密钥写入设备时,将通过将预期的 CRC32 值通过 JTAG 写入设备来启动密钥完整性检查。设备(内部)会根据存储的密钥计算实际的 CRC32 完整性检查,并将其与刚刚通过 JTAG 端口接收到的预期 CRC32 进行比较。然后,设备将通过/失败类型的结果(而不是实际的密钥数据)写入 JTAG 端口,以表示完整性状态。移除密钥的物理读回路径可提高存储密钥的安全性。

BBRAM关键编程解决方案包括:

- Vivado设备编程器工具和 JTAG 电缆的使用 注意:对于基于 BBRAM 的密钥,在写入密钥之前,BBRAM 中的现有密钥将被清零(擦除并验证)。

eFUSE 密钥编程解决方案包括:

- AMD编程

- AMD测试中心的全自动在线 ATE 流程

- 安全编程,适用于中到高容量——采用统一设置

- 安富利编程

- 安全性、处理、序列化和其他差异化的机会

- 非常适合从中等音量到低音量进行编程

- 客户制造流程

- 第三方工具,或集成在设计中BBRAM 和 eFUSE 的内部编程(XAPP1283),使用AMD编程技术

- 非常适合定制要求,包括高度机密信息处理

- 防止或清除 FPGA 的配置设计,以最大限度地减少 FPGA 内的电源噪声。

- 如果可能,请停止板级系统时钟以最大限度地减少系统电源噪声。

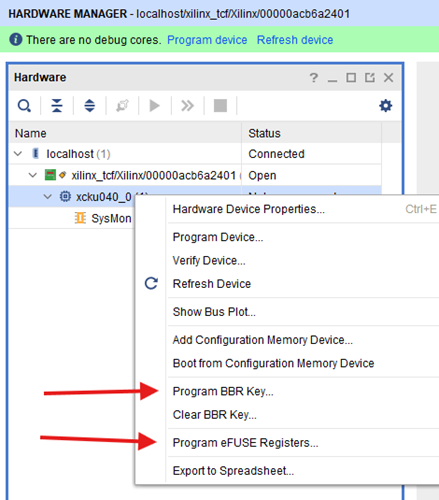

使用Vivado硬C,右键单击UltraScale FPGA 以选择程序 BBR 密钥...或 程序 eFUSE 寄存器...,具体取决于您之前选择的存储选项(见下图)。

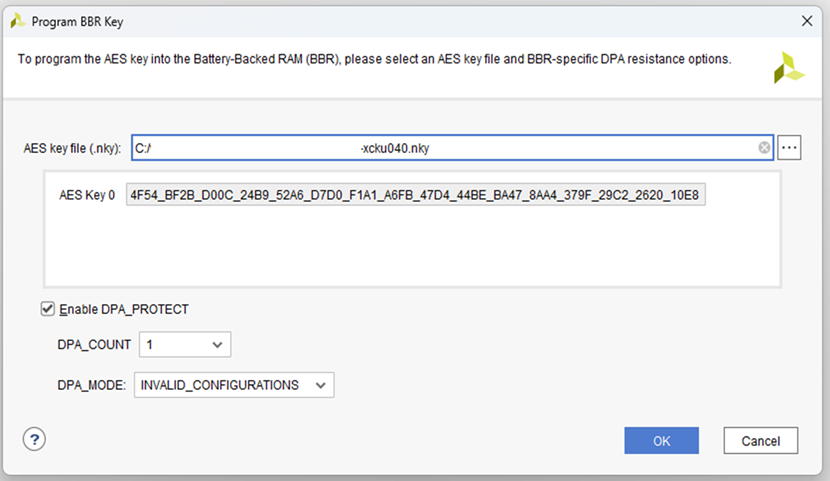

BBRAM

选择“Program BBR Key...”后,您可以浏览到项目目录中最近生成的 NKY 文件。添加 NKY 文件后,您还可以仔细检查密钥值,并确认这是您打算编程到设备中的 AES 密钥。(参见下图。)

KeyObfuscate软件会自动设置 eFUSE 或 BBRAM 中的混淆密钥标志。 启用 DPA_PROTECT 复选框启用 BBRAM 配置计数 DPA 保护机制。

- DPA_COUNT 指定配置计数器的初始加载值。一旦计数达到 0,BBRAM 就会被擦除。

- DPA_MODE 指定在什么条件下应减少 DPA_COUNT。有两个选项:INVALID_CONFIGURATIONS(典型的 DPA 设置)和 ALL_CONFIGURATIONS(每次配置时都会减少 DPA_COUNT 的计数,以确保设备有固定数量的配置可供使用)。

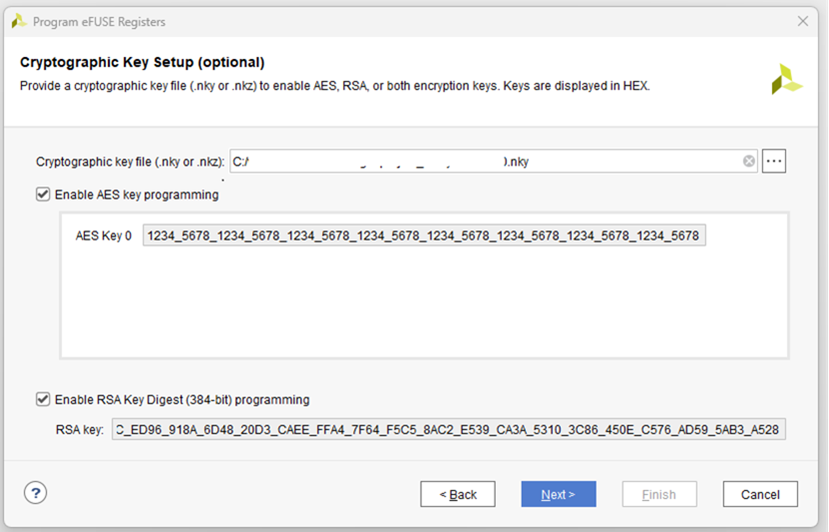

电子保险丝

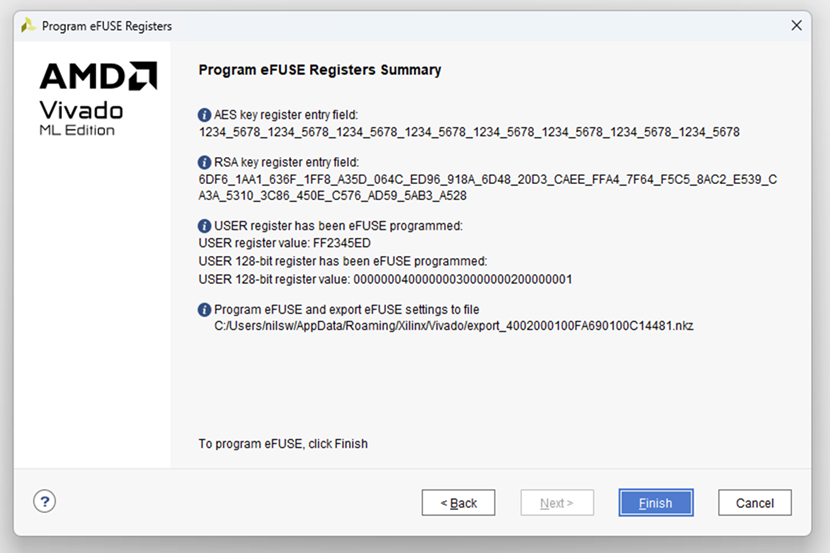

当您选择“编程 eFUSE 寄存器...”时,将出现一个向导,引导您完成选择 NKY 文件和要编程的各种 eFUSE 寄存器的过程。添加 NKY 或 PEM 文件后,您还可以仔细检查密钥值,并确认这些密钥是您打算编程到器件中的 AES 和 RSA 密钥。(参见下图。)

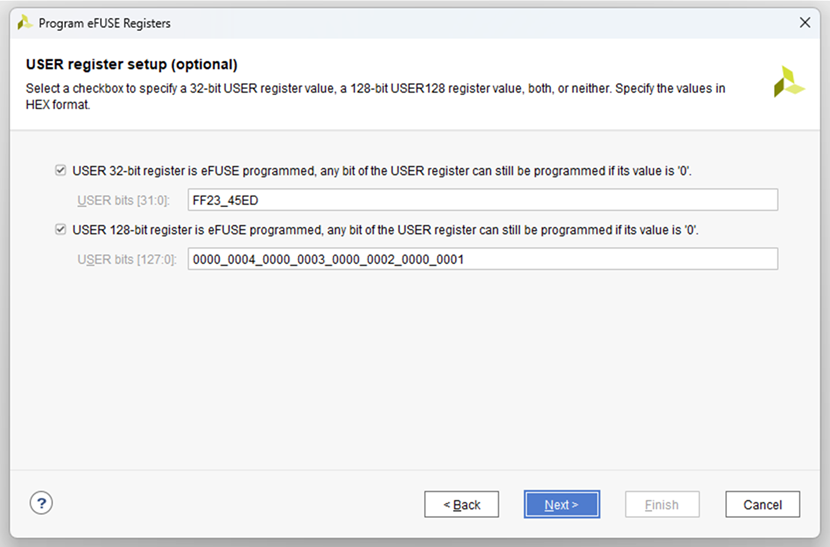

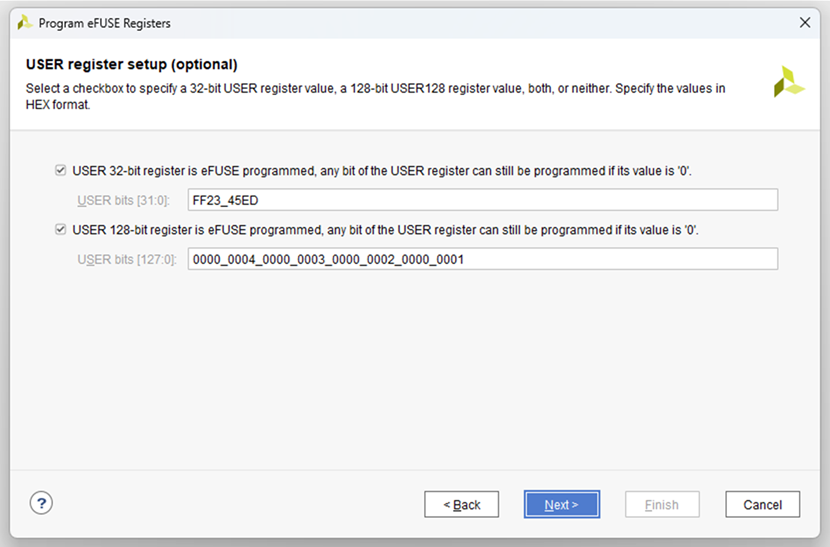

用户寄存器设置屏幕如下图所示。您可以指定一个唯一的 32 位和/或 128 位值,并将其编程到 FUSE_USER 寄存器位中。这些寄存器可以通过 eFUSE_USR 原语从 FPGA 逻辑读取。

控制寄存器设置屏幕如下图所示。您可以通过该屏幕选择要编程的 FUSE_CNTL 寄存器位。这些位通过禁用不同 eFUSE 控制寄存器上的读写操作来确保安全性。

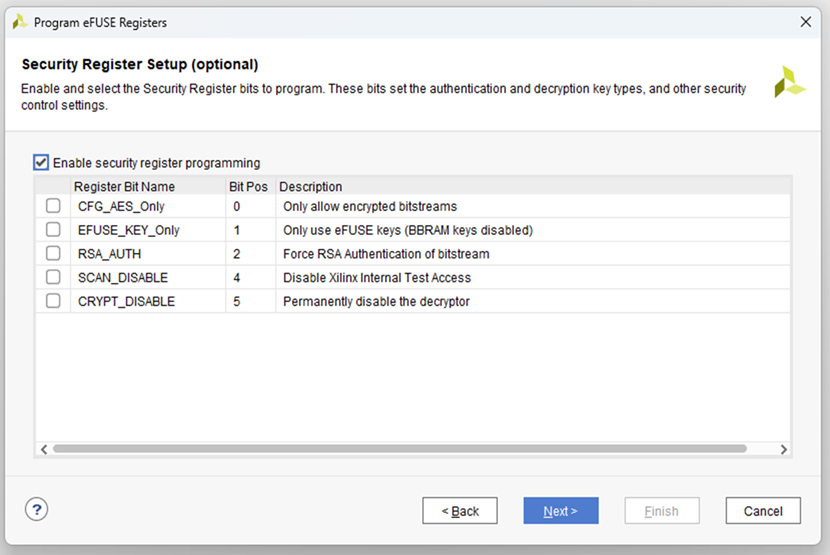

安全寄存器设置屏幕如下图所示。您可以选择要编程的 FUSE_SEC 寄存器位。这些位通过仅允许加密比特流或启用 RSA 身份验证来提供额外的安全性。

KeyObfuscate软件会自动设置 eFUSE 或 BBRAM 中的混淆密钥标志。

加载加密比特流

使用正确的加密密钥对器件进行编程后,即可使用加密比特流进行配置。使用加密比特流进行配置后,无论比特流安全设置如何,都无法通过 JTAG 或 SelectMAP 回读读取配置存储器。尽管器件持有加密密钥,但可以使用非加密比特流配置器件(仅当 FUSE_SHAD_SEC[0] 位未编程时),并且仅在 INIT_B 或 PROGRAM_B 置位后才能使用,从而清除配置存储器。在这种情况下,密钥将被忽略。使用非加密比特流进行配置后,可以进行回读(如果 write_bitstream 安全设置允许)。但是,仍然无法从器件中读出加密密钥,从而防止使用特洛伊木马比特流破解UltraScale FPGA 加密方案。

所有受支持的配置方法均不受加密影响。UltraScale FPGA 不允许同时使用压缩和 RSA 身份验证创建比特流。加密比特流可以通过任何配置接口传输:JTAG、串行、SPI、BPI、SelectMAP 或 ICAPE3。配置完成后,如果不切换 PROGRAM_B 引脚、循环上电或发出 IPROG 或 JPROGRAM 指令,则无法重新配置器件。即使启用加密,Fallback 和 IPROG 重新配置仍会启用。Fallback 和 IPROG 重新配置映像可以是加密的,也可以是未加密的。可通过 ICAPE3 原语进行读回。如果 V BATT或 V CCAUX保持稳定,则上述事件均不会重置 BBRAM 密钥。

如果加密比特流中的密钥与器件中存储的密钥不匹配,则会导致配置失败,此时 INIT_B 引脚将先脉冲为低电平,如果启用了回退功能,则脉冲回升至高电平,而 DONE 引脚则保持低电平。加密比特流支持高级配置解决方案,例如串联配置和部分重配置。部分比特流可以以未加密的形式传输到 ICAP,也可以加密(使用相同的 AES 密钥)传输到任何配置端口,只要后者未被设计人员明确禁止。设置安全级别 2(通过 set_property BITSTREAM.READBACK.SECURITY Level2 [current_design] 实现)或将 FUSE_SHAD_SEC[0] 的“CFG_AES_Only”位编程为 ,1可防止通过外部配置端口进行部分重配置。

eFUSE 编程一般建议

对 eFUSE 编程项目应用以下建议:

- 要求:使用Vivado Design Suite 2017.1 或更新版本。

- 建议:如果电路板设计允许,则在 eFUSE 编程期间将 FPGA 配置模式引脚设置为仅 JTAG 设置。

- 要求:使用单独的 eFUSE 编程操作,例如,单独通过编程 eFUSE GUI 向导或单独的 Tcl 命令,按照以下顺序编程适用的 eFUSE 值和选项:

- 编程 eFUSE 操作步骤 #1:编程 NKY 值(AES、RSA)和 FUSE_USER 值。

- 编程 eFUSE 操作步骤 #2:(如果适用)对安全寄存器 (FUSE_SEC) 选项进行编程,JTAG 禁用除外。

- 编程 eFUSE 操作步骤 #3:(如果适用)对控制寄存器(FUSE_CNTL)选项进行编程,但 W_DIS_CNTL(写入禁用控制寄存器)除外。 注意:如果需要在最后一步(5)中对安全寄存器 JTAG 禁用选项进行编程,请不要对控制寄存器 W_DIS_SEC 选项进行编程。

- 编程 eFUSE 操作步骤 #4:(如果适用)编程控制寄存器 W_DIS_CNTL(写入禁用 FUSE_CNTL 寄存器)。请参阅 Vivado Design Suite 用户指南:编程和调试(UG908)。

- 最后一次编程 eFUSE 操作步骤:(如适用)编程安全寄存器 JTAG 禁用。请参阅Vivado Design Suite 用户指南:编程和调试( UG908 )。

- 建议:对于第一个编程的设备,在完成上述每个步骤后验证 eFUSE 结果,然后在完成所有步骤后重新验证 eFUSE 结果,以确保完整的 eFUSE 编程过程的最终结果符合预期。

- 如果已编程 AES 和/或 RSA 值,则验证设备是否成功加载 AES 加密和/或 RSA 签名的比特流。

- 如果 FUSE_USER 值已被编程,则验证您是否读取了正确的 JTAG FUSE_USER 和/或 EFUSE_USER 原始值。

- 如果对 FUSE_SEC 设置进行了编程,则验证所选设置是否具有正确的设备行为。

- 如果对 FUSE_CNTL 设置进行了编程,则检查Vivado中生成的 REGISTERS.EFUSE.FUSE_CNTL 值以验证设置,并检查Vivado中受读保护的 REGISTER.EFUSE.* 寄存器是否显示您的实际值。 注意:预计Vivado将显示一些 FUSE_CNTL 保留位位置,这些位置之前已由AMD工厂编程为“1”。

- 根据步骤 5 的选择,验证您是否可以访问设备 JTAG。

硬件验证

- 使用Vivado 2017.1 或更高版本生成比特流:未加密的比特流、使用您的个性化密钥的加密比特流、使用全一密钥的加密比特流以及使用全零密钥的加密比特流。

- 检查生成的比特流以验证是否发生了加密。

- 检查硬件:使用Vivado Device Programmer 连接到 FPGA,通过 JTAG 下载未加密的 bit 文件。验证设计是否按预期运行。

- 测试 FPGA 解密器:下载使用全零密钥(用于 eFUSE)加密的 .bit 文件。

- 按照上一节中的建议,通过 JTAG 对 AES 密钥进行编程。(如果使用 eFUSE,请先使用 BBRAM 密钥执行步骤 5 和 6,进行验证检查;如果一切正常,则对 eFUSE 进行编程以进行最终测试。)

- 测试密钥:使用您的个性化密钥下载加密的 .bit 文件。

- 测试密钥:下载使用全零密钥加密的 .bit 文件(预计失败)。

- 测试密钥设置:下载未加密的 .bit 文件(结果可能因安全设置而异)。

- 检查密钥安全性:检查密钥是否具有读保护。

结论

本应用笔记介绍了UltraScale FPGA AES 加密和身份验证标准。它介绍了不同密钥存储选项的优缺点。最重要的是,它提供了一个简单的指南,指导您如何创建加密的比特文件以及加密和身份验证密钥,以及如何使用Vivado软件将这些文件编程到UltraScale FPGA中。

查找其他文档

技术信息门户

AMD技术信息门户是一款在线工具,可通过 Web 浏览器提供强大的文档搜索和导航功能。要访问技术信息门户,请访问https://docs.amd.com。

文档导航器

文档导航器 (DocNav) 是一款已安装的工具,可让您访问AMD自适应计算文档、视频和支持资源,并可进行筛选和搜索以查找信息。要打开 DocNav,请执行以下操作:

- 从AMD Vivado™ IDE 中,选择 帮助>文档和教程。

- 在 Windows 上,单击“开始”按钮并选择 Xilinx 设计工具> DocNav。

- 在 Linux 命令提示符下,输入

docnav。

设计中心

AMD设计中心提供按设计任务和其他主题组织的文档链接,您可以使用这些链接了解关键概念并解答常见问题。访问设计中心的方法如下:

- 在 DocNav 中,单击设计中心视图选项卡。

- 转到设计中心网页。

参考

这些文档提供了对本指南有用的补充材料:

- 高级加密标准 (AES) ( FIPS PUB 197 )

- 伽罗瓦/计数器操作模式(GCM)(规范)

- UltraScale 架构配置用户指南( UG570 )

- Vivado Design Suite 用户指南:编程和调试(UG908)

- 使用 UltraScale 和 UltraScale+ FPGA 开发防篡改设计( XAPP1098 )

- OpenSSL(www.openssl.org)

- BBRAM 和 eFUSE 的内部编程( XAPP1283 )

- UltraScale FPGA RSA 身份验证和支持配置模式( XCN15038 )

- UltraScale/UltraScale+ FPGA 系列设计咨询:RSA 身份验证漏洞 (JustSTART) ( 000036039 )

- UltraScale RSA 身份验证的设计咨询 - 使用 RSA 身份验证的 UltraScale 设备在使用较小配置接口宽度时将无法通过比特流身份验证(AMD设计咨询65792)

)

)

)