- 前置

- MOS结构基础

- 理想MOS结构回顾

- Delta-耗尽层模型

- 非理想因素

- MOSFET基础

- 参数与定义

- 定性分析

- 理想长沟道MOSFET

- 缓变沟道近似(GCA)

- 反型层电荷密度和阈值电压

- 直流I-V特性

- 理想MOSFET的电荷-电压特性

- 理想MOSFET的频率响应

- 非理想效应

- 沟道长度调制效应(CLM)

- 体效应(Body effect)

- 亚阈值电流

- 非理想MOSFET

- MOSFET阈值电压的设计

- 小尺寸效应

- 如何抑制小尺寸效应

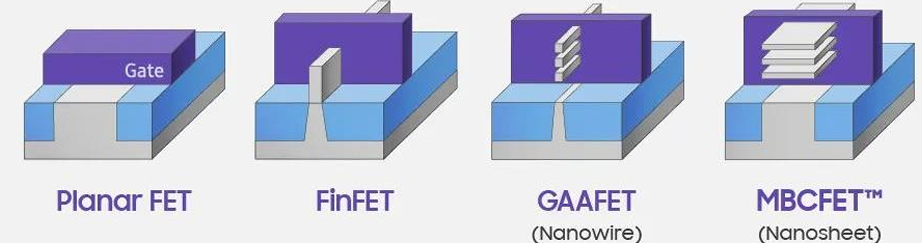

- 现代MOSFET 结构

前置

半导体物理知识(能带模型);半导体器件知识基础(各种近似;BJT)

所讨论的MOSFET无特别说明均为p衬底的。

MOS结构基础

理想MOS结构回顾

理想MOS结构是一个简单的二端器件,由半导体衬底和金属极板之间夹一薄层半导体氧化层制成。

理想MOS结构假设:

- 金属与半导体之间的功函数差为零

- 氧化层内没有任何电荷

- 氧化层与半导体界面不存在任何界面态

当两端MOS结构加上偏压后,会在金属和半导体层内产生数值相等、符号相反的感生电荷。在金属中,感应电荷\(Q_G\)分布在金属表面一个原子层的厚度内;在半导体内,电荷\(Q_S\)分布在具有一定表面厚度的表面层中,称为空间电荷区。栅极电压等于氧化层两端的电压和半导体空间电荷区两端的电压之和:\(V_G=-Q_S/C_{OX}+\phi_S\)

在能带模型中,外加偏压导致空间电荷区能带弯曲。用表面势

表征能带弯曲程度。

半导体体内的费米势定义为

使半导体表面强反型时的栅极电压称为MOS结构的阈值电压\(V_T\)。注意与MOSFET的阈值电压区分。

Delta-耗尽层模型

Delta-耗尽层模型假设:

- 当表面势\(0<\phi_S\le 2\phi_F\)时,表面处于耗尽状态;在耗尽区中,\(n=p=0\),耗尽层近似成立;

- 当表面势\(\phi_S\ge 2\phi_F\)后,表面开始强反型,表面势开始不随栅压变化,耗尽层宽度和耗尽层电荷开始维持不变;反型层载流子随栅压的增加而指数增加;

- 反型层位于半导体表面,其厚度可忽略。

反型层载流子被限制在表面能量最低的一个狭窄区间,所以反型层也称为沟道。

由Delta-耗尽层模型,表面耗尽时,

两式联立可求得\(\phi_S\)。

表面强反型后,

耗尽层宽度\(W=\sqrt{\dfrac{2\varepsilon_0 K_S}{qN_A}2\phi_F}\equiv W_T\)

单位面积的耗尽层电荷\(Q_{dep}=-qN_AW_T\equiv Q_{depmax}\)

单位面积反型层电荷\(Q_{inv}=Q_S-Q_{depmax}\)

表面强反型后,\(V_G=-Q_S/C_{OX}+2\phi_F\)

解得反型层电荷

其中

非理想因素

实际MOS结构中存在各种非理想因素,如栅金属半导体之间有功函数差、栅氧化层中以及栅氧化层-半导体界面存在各种电荷。这些非理想因素会导致在栅压为零时半导体表面能带弯曲。各种非理想因素对理想MOS结构的影响通常用平带

电压\(V_{FB}\)表示。\(V_{FB}\)定义为:使能带恢复到平直状态所需要的外加栅电压。

计入平带电压后,实际MOS结构的阈值电压为\(V_T=V_{FB}\pm 2\phi_F \pm \sqrt{4q\varepsilon_0 K_S N_A \phi_F}/C_{OX}\)。对于n衬底取负号。

MOSFET基础

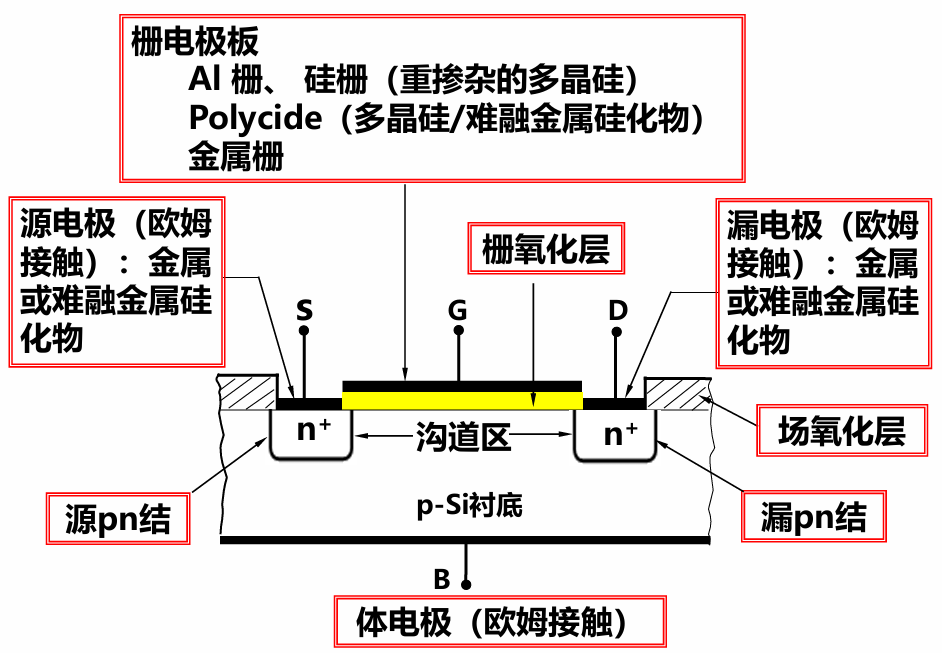

参数与定义

结构参数:

- 沟道长度\(L\)

- 沟道宽度\(W\)

- 栅氧化层厚度\(t_{ox}\)

- 衬底掺杂浓度\(N_A\)

- 源/漏pn结结深\(r_j\)

通常以源端为电压参考点,\(I_D=f(V_{GS},V_{DS},V_{BS})\).源和衬底一般是短接在一起的。

MOSFET分类:

按照沟道类型:

- nMOS:衬底为p型,源/漏区为重掺杂的n型区, 沟道载流子为电子;

- pMOS:衬底为n型,源/漏区为重掺杂的p型区,沟道载流子为空穴。

按照工作模式:

- 增强型:零栅压时不存在导电沟道;

- 耗尽型:零栅压时存在导电沟道。

后续分析无特别说明均为nMOS。

定性分析

施加栅压\(V_G\)在沟道区形成反型层, 施加漏压\(V_D\)使反型层载流子从源到漏运动而形成漏极电流\(I_D\)。

若\(V_G<V_T\),则沟道处于耗尽状态,\(I_D\approx 0\);若\(V_G>V_T\),则沟道强反型,反型层把源区与漏区连通,此时若\(V_D>0\),则漏电流\(I_D\neq 0\),且在合适偏置下,\(I_D\)与\(V_D\)无关,且\(V_G\)越大\(I_D\)越大,以此实现放大功能。

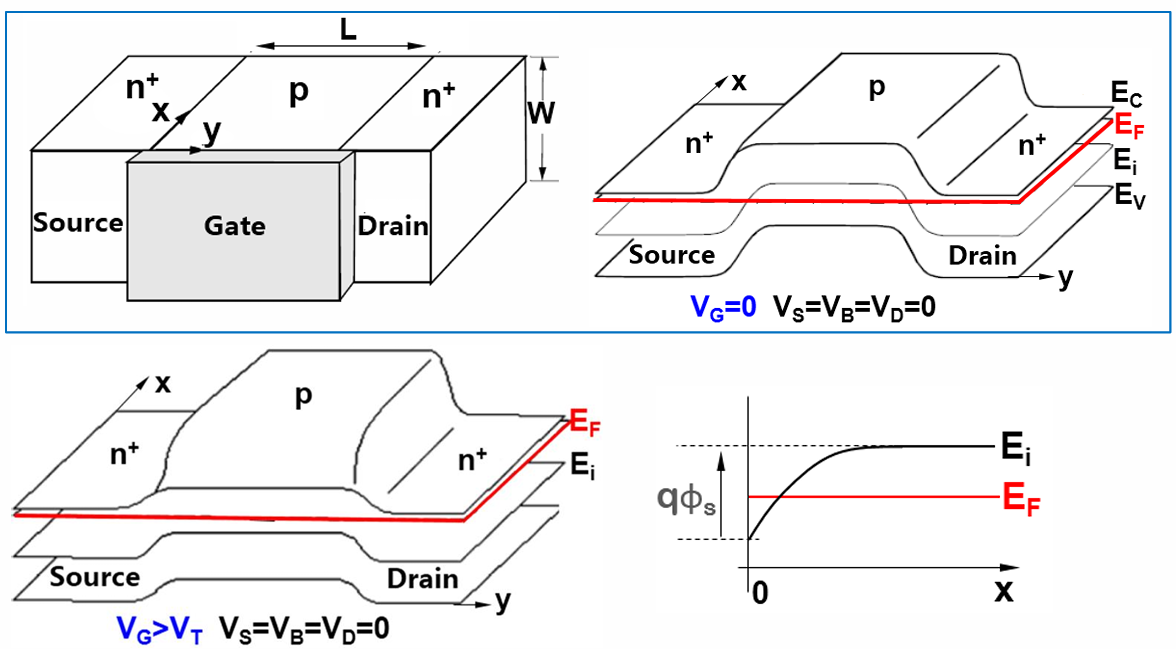

栅极偏置电压\(V_G\)的作用(\(V_S=V_B=V_D=0\))

栅压使沟道区能带在x方向弯曲, 在半导体表面形成空间电荷区

半导体表面处于平衡态, 器件可等效为一个MOS电容。与两端MOS电容不同的是, n+区提供反型层载流子。

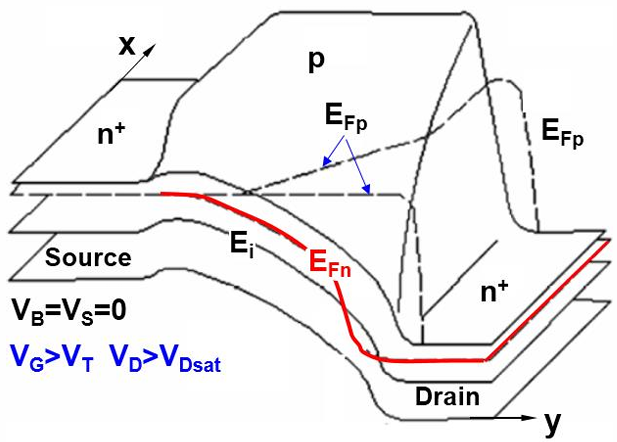

漏极偏置电压\(V_D\)的作用(\(V_S=V_B=0\))

沟道反型后, 施加漏压会导致沟道区能带沿沟道y方向发生弯曲, 半导体表面处于非平衡态; 栅下的电场也变成二维。

沟道区多子的准费米能级(这里是\(E_{Fp}\))基本不变,与体内相同,而漏压\(V_D\)引起少子准费米能级从源到漏降低。

定义沟道电势\(V_{CS}(y)\) 为沟道区\(y\)处 少子的准费米能级与多子的准费米能级的差,即

在\(V_{SB}=0\)时,\(V_{CS}(y=0)=0,V_{CS}(y=L)=V_{DS}\).

因此, 在表征MOSFET的表面空间电荷区时,需要两个参量:一个是表面势,另一个是沟道电势。

在沟道反型后, 施加漏压会导致:

- 反型层载流子从源到漏流动,形成漏极电流\(I_D\)。

- 反型层与体内多子不再有统一的费米能级,半导体表面处于非平衡态。

- 沟道区的电场是二维的。

- 反型层厚度从源到漏逐渐减弱,而耗尽层从源到漏逐渐展宽。

理想长沟道MOSFET

理想MOSFET条件:

- 衬底均匀掺杂,MOS结构是理想的(非理想因素等效为\(V_{FB}\))

- 反型层载流子运动是一维的

- 忽略载流子复合与产生,即直流时\(\nabla\cdot J=0\)

- 忽略pn结的反向泄漏电流和源漏区的体电阻。

- 载流子的迁移率为常数。

- 缓变沟道近似成立。

缓变沟道近似(GCA)

缓变沟道近似假设:沟道内平行于沟道方向的电场的变化远小于垂直于沟道方向的电场的变化, 即\(\dfrac{\partial \mathscr E_x(x,y)}{\partial x} \gg \dfrac{\partial \mathscr E_y(x,y)}{\partial y}\)。在此假设下,沟道区的泊松方程由二维退变为一维:

GCA认为MOSFET可以分解成两个一维结构:垂直于沟道方向的电场由栅压\(V_G\)控制, 而平行于沟道方向的电场由漏电压\(V_D\)控制, 这两个电场近似独立, 没有强的相互作用。沟道区的反型层和耗尽层电荷都是栅压产生的, 漏压仅使反型层载流子从源到漏运动。

为了使GCA成立, 通常在MOSFET的设计中, 应使\(L\gg t_{ox}\)。

长沟道器件是指器件的沟道长度远大于源pn结和漏pn结耗尽区宽度之和。在长沟道器件中,如果

\(L\gg t_{ox}\),则GCA在沟道大部分区域是成立的。

反型层电荷密度和阈值电压

根据GCA,沟道区的泊松方程为

对于半导体表面附近(令\(x=0\)),在\(\phi_s\gg kT/q\)的近似下,半导体表面处单位面积电荷

强反型时,\(\phi_s(y)\approx 2\phi_F+V_{CS}(y)\)

使 沟道源端\((y=0)\) 处开始强反型时所需的栅源电压\(V_{GS}\)定义为 MOSFET的阈值电压\(V_T\) ,在源体短接时,nMOS的阈值电压

数值上和MOS结构的阈值电压一致。

直流I-V特性

基本方程

由于\(I_D\)在y方向上处处相等(GCA推论),可得

平方律模型

假设表面处于强反型,\(\phi_s(y)= 2\phi_F+V_{CS}(y)\)

电荷薄层假设体内电荷分布集中于半导体表面,但先暂且忽略漏电压对栅下耗尽层电荷的影响,即

上式仅在\(V_{DS}<V_{GS}-V_T\)的条件下成立。当\(V_{DS}=V_{GS}-V_T\)时,沟道漏端反型层电荷

即在此条件下, 反型层在漏端消失了, 这种现象称为沟道夹断(pinch-off)。

沟道被夹断意味着此时GCA失效,电流达到峰值,对应的\(V_{DS}\)称为饱和电压\(V_{Dsat}\) ,对应的电流称为饱和电流\(I_{Dsat}\)。

夹断后, 漏压再增加时, 夹断点会向源端移动, 导电沟道和漏端分离, 它们之间存在一个耗尽区(称为夹断区), 所增加的漏压全部降落在夹断区上,而源与夹断点之间的反型层上的电压仍保持为\(V_{Dsat}\)。

假设MOS器件处于夹断状态, 其沟道长度为\(L'\), 沟道两端的电压为\(V_{Dsat}=V_{GS}-V_T\), 则其电流为

当\(L\gg \Delta L\)时, 漏极电流主要取决于源与夹断点之间的反型层载流子的输运, 受夹断区的影响很小,\(I_D=I_{Dsat}\),称漏电流饱和了,器件工作在饱和区。

在MOSFET的结构中, 源和漏是对称的, 在设计和制造上没有区别, 源和漏是可以互换的。源和漏的定义取决于使用时所加的偏压: 对于nMOS, 漏极的电压高于源极的电压;对于pMOS, 漏极的电压低于源极的电压。

I-V特性

对于nMOSFET,

其中\(V_{Dsat}=V_{GS}-V_T\)为饱和电压,\(V_T\)为阈值电压,在\(V_{SB}=0\)时,\(V_T=V_{FB}+2\phi_F+\sqrt{4q\varepsilon_0 K_S N_A \phi_F}/C_{ox}\).

当\(V_{GS}\le V_T\)时, 平方率模型假设\(I_D=0\), 此时我们说器件工作在截止区。

\(I_D\sim V_{GS}\)称为MOSFET的转移特性,它反映了栅源电压\(V_{GS}\)对漏极电流\(I_D\)的控制能力。

共源极连接时\(I_D\sim V_{DS}\)曲线称为MOSFET的输出特性, 反映了在栅压恒定时, \(I_D\)随漏极电压\(V_D\)的变化规律。

根据所加的\(V_{DS}\)大小,输出特性分为三个区域:线性区,饱和区,击穿区:

- \(V_{DS}\le V_{GS}-V_T\)时,器件工作在线性区。在线性区,沟道从源到漏是连续的。

- \(V_{DS}> V_{GS}-V_T\)时,器件工作在饱和区,沟道漏端被夹断,夹断点随\(V_{DS}\)增加向源端移动。

- \(V_{DS} \gg V_{GS}-V_T\)时,器件进入击穿区,\(I_D\)随\(V_{DS}\)增加而急剧增加。

在线性区,如果\(V_{DS}\ll 2(V_{GS}-V_T)\),则

此时, \(I_D\)是\(V_{DS}\)的线性函数, 表明源漏之间的沟道可用一个线性电阻表示:

因此, 在\(V_{DS}\ll 2(V_{GS}-V_T)\)时(称为深线性区), MOSFET可以作为一个由\((V_{GS}-V_T)\)控制的电阻。

在饱和区, \(V_{GS}\)由两部分构成, 一部分形成沟道, 另一部分支持所需要的电流。称\(V_{GS}-V_T\)为过驱动电压.

对平方律模型的改进:平方根近似

式中\(C_{sT}=\sqrt{\dfrac{q\varepsilon_0 K_S N_A}{4\phi_F}}\)

由此得到反型层电荷

,其中\(m=1+C_{sT}/C_{ox}\)称为体电荷因子。

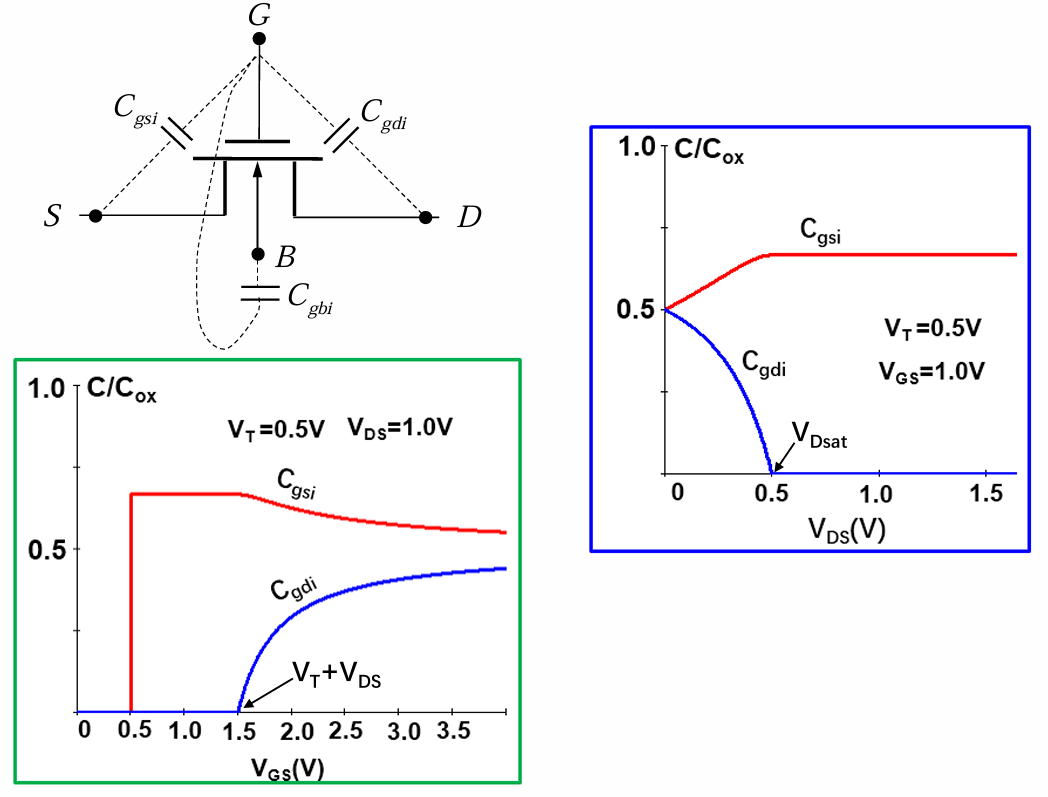

理想MOSFET的电荷-电压特性

在理想MOSFET中, 有两类存储电荷:

- 源漏pn结之间的沟道区存储的电荷, 由反型层电荷\(Q_{inv}\)和耗尽层电荷\(Q_{dep}\)组成, 这些电荷称为本征电荷, 相应的电容称为本征电容。

- 源衬pn结耗尽区电荷\(q_{JSB}\), 漏衬pn结的耗尽区电荷\(q_{JDB}\) , 相应的电容就是pn结的势垒电容\(C_{JSB}\)和\(C_{JDB}\)。

器件的电荷存储效应决定了MOSFET的动态响应。

本征电荷

耗尽层电荷

利用平方律模型里\(I_D\)和\(\mathrm d V_{CS}/\mathrm dy\) 的关系,得反型层电荷

在饱和区,

沟道渡越时间:载流子越过沟道所需的平均时间

准静态近似:假设端电压的变化足够慢, 使器件内部按准静态工作, 即存储电荷能够跟得上端电压的变化。

根据准静态近似, 在动态时, 本征电荷与端电压之间的关系与直流时的相同。

通常把本征电荷分解为三个集总电荷\(q_D\)、\(q_S\) 和 \(q_B\).\(q_G=q_D+q_S+q_B\).

本征电容:端电压变化时引起的栅电荷变化。

Meyer电容模型:把本征电容分解为三个集总电容,分别定义为

栅源电容

栅漏电容

栅体电容

Meyer电容模型假设:电容是互易的,栅下的耗尽层电荷沿沟道方向为常数。

在线性区

在饱和区

在耗尽区

非本征电容:

- 结横向扩展导致的栅覆盖电容:栅源覆盖电容,栅漏覆盖电容,栅体覆盖电容

- 源、漏pn结电容

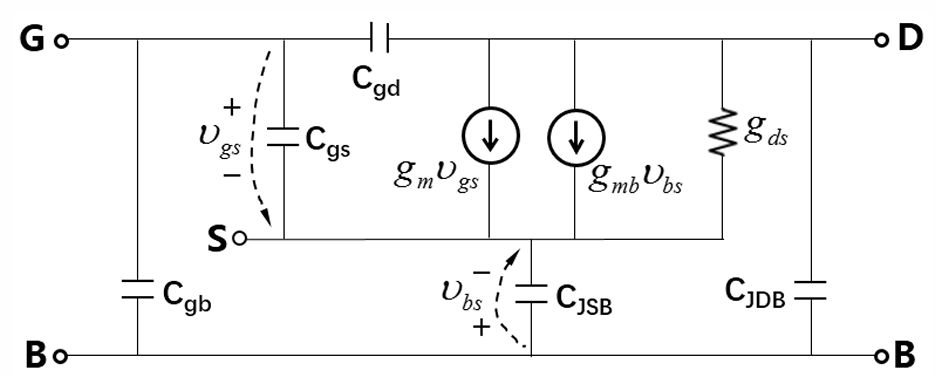

理想MOSFET的频率响应

小信号工作时,\(i_D(t)\approx I_D(V_{GS},V_{DS},V_{BS})+i_d(V_{GS},V_{DS},V_{BS},v_{GS},v_{DS},v_{BS})\)

忽略高次项,并定义:

小信号跨导

小信号漏电导

小信号衬底跨导

则电流的交流分量为

栅跨导是MOSFET转移特性曲线的斜率, \(g_m\)反映了\(V_{GS}\)对漏极电流\(I_D\)的控制能力。

漏电导是MOSFET输出特性曲线的斜率, \(g_{ds}\)反映了漏极电流\(I_D\)随\(V_{DS}\)的变化而变化的情况。

衬底跨导\(g_{mb}\)反映了漏极电流\(I_D\)随衬底偏压\(V_{BS}\)的变化而变化的情况。

这些参数可由I-V特性求得。

本征截止频率

使共源级输出短路电流增益(源漏电流与栅电流的比值)为1时的频率称为本征截止频率。

当器件工作在饱和区,

提高截止频率的方法:

- 减小沟道长度;

- 提高载流子迁移率;

- 在结构和工艺上尽量减小寄生电容;

沟道载流子延迟时间\(\tau_d = (C_{gs}+C_{gd})/g_m\)

非理想效应

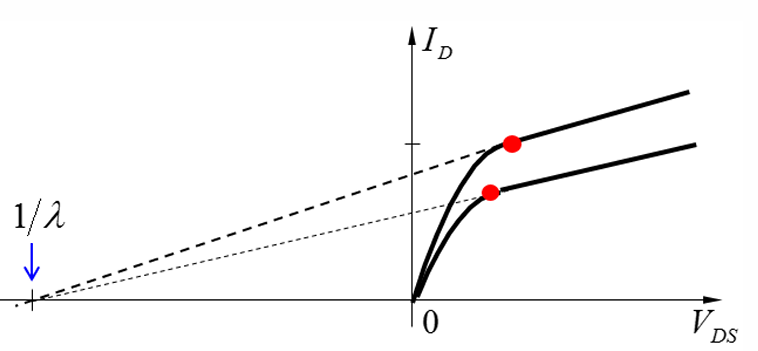

沟道长度调制效应(CLM)

在饱和区, 随着\(V_{DS}\)的增加,夹断点向源端移动, 导电沟道长度\(L'\)随漏压的增加而减小, 这种现象称为沟道长度调制效应。

考虑到此效应后, 在饱和区, \(I_D\)会随\(V_D\)的增加而增加。

对于一个精心设计的MOS器件,\(\Delta L \ll L\),假设\(\Delta L\)与\(V_{DS}\)成正比,即\(\Delta L=\lambda'V_{DS}\),其中\(\lambda'\)是一个与\(L\)无关工艺参数。定义沟道长度调制系数 \(\lambda = \lambda'/L\),对于给定的工

艺, \(\lambda\) 与沟道长度成反比, 沟道越长, \(\lambda\) 越小。

考虑到沟道长度调制效应后,饱和区电流\(I_D=I_{Dsat}(1+\lambda V_{DS})\),漏电导\(g_{ds}=\lambda I_{Dsat}\),跨导\(g_m=\mu_n C_{ox} \frac{W}{L} (V_{GS}-V_T)(1+\lambda V_{DS})\).

体效应(Body effect)

衬底偏压\(V_B\)通过影响栅下耗尽层电荷影响阈值,随着\(V_{SB}\)的增加, 阈值电压\(V_T\)增大,

衬底偏压对阈值电压的影响称为体效应或背栅效应。

定义体效应因子

阈值电压变化量

体效应通常是不希望有的, 器件设计中通过减小栅氧的厚度以及降低衬底的掺杂浓度来削弱体效应。也可以通过衬底偏压来调节MOSFET的阈值电压。

亚阈值电流

平方律模型认为, 当栅源电压低于\(V_T\)时, \(I_D=0\)。实际中的MOSFET, 当\(V_G<V_T\)时, 表面是弱反型的,相应的\(I_D\) 虽然很小但并不等于零, 此电流称为亚阈值电流。弱反型区也称为亚阈值区。

表面弱反型时, \(V_{DS}\)几乎全部降落在反偏的漏衬pn结耗尽区上, 漏极电流的漂移分量可以忽略, 但是反型层载流子浓度沿沟道方向有梯度, 因此亚阈值电流是扩散电流。

亚阈值电流方程

长沟道MOSFET亚阈值电流的特点:

- 亚阈值电流随\(V_{GS}\)呈指数变化。

- \(V_{DS}\)大于3个热电势后, 亚阈值电流与\(V_{DS}\)无关。

- 亚阈值电流对温度有强烈的依赖关系。

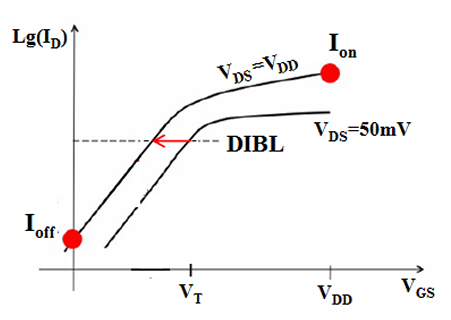

亚阈值摆幅

亚阈值摆幅\(S\)定义为亚阈值区\(\lg(I_D) \sim V_{GS}\)曲线斜率的倒数, 表示亚阈值电流减小一个数量级所需的栅压的变化量。

\(S\)量化了亚阈值电流如何随栅压变化, \(S\)越小, \(V_G\)对\(I_D\)的控制能力越强, 开关特性越好。

亚阈值摆幅下限

减小亚阈值摆幅\(S\):减小\(t_{ox}\)、减小衬底掺杂浓度。

非理想MOSFET

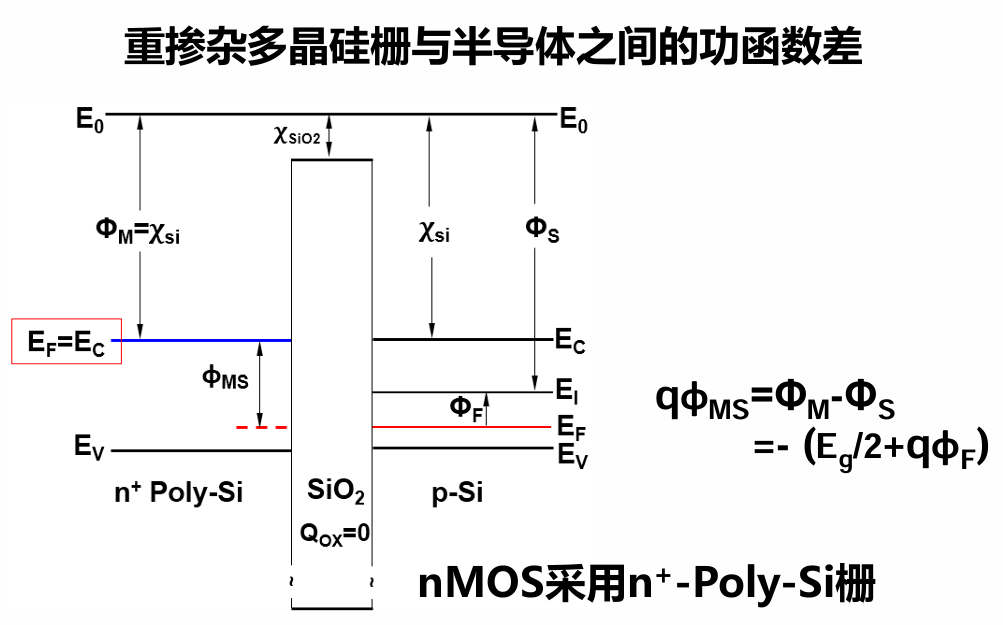

MOSFET阈值电压的设计

MOSFET阈值电压定义为使源端开始强反型时所需的栅源电压。

对于nMOS,\(V_T=V_{FB}+ 2\phi_F + \sqrt{4q\varepsilon_0 K_S N_A \phi_F}/C_{ox}\),

对于pMOS,\(V_T=V_{FB}- 2\phi_F - \sqrt{4q\varepsilon_0 K_S N_A \phi_F}/C_{ox}\),

其中\(\phi_F=\dfrac{kT}{q}\ln\left(\dfrac{N_B}{n_i}\right)\),\(V_{FB}=\phi_{MS}-Q_{ox}/C_{ox}\),\(C_{ox}=\dfrac{\varepsilon_0 K_{ox}}{t_{ox}}\),\(\phi_{MS}\)为栅材料与半导体之间的功函数差,\(Q_{ox}\)为氧化层中位于Si-SiO2界面处的等效薄层电荷面密度, 代表了氧化层中各种电荷(固定正电荷、可动正电荷、陷阱电荷、界面陷阱电荷)的影响。

\(\phi_{MS}\)是完全可以预测的,而\(Q_{ox}\)与晶向和氧化层生长工艺有关。\(Q_{ox}\)会使阈值电压不稳定, 因此, 其值要尽可能小。

阈值电压的控制和调整

在实际中,当\(t_{ox}\)、\(N_A\)和栅电极材料确定后,由上述公式计算得到的阈值电压可能不能满足对阈值电压大小的要求,因此在器件的制造中必须调整阈值。通常是采用离子注入工艺, 向沟道区表面处注入一定数目的硼或磷离子来调整阈值电压, 其实质是改变沟道区氧化层界面附近衬底的杂质浓度。

阈值调整注入的深度一般比较浅, 通常用Delta函数近似实际的分布, 即认为注入的杂质全部位于SiSiO2界面无限薄的薄层硅中。

由于阈值调整注入引起的阈值电压的变化为:

其中\(D_I\)为注入剂量, 表示单位面积注入的离子数目,对于受主杂质取正号,施主杂质取负号。

MOS器件偏置在耗尽或反型时,注入的杂质会叠加到半导体表面附近的电离杂质电荷上,从而改变阈值电压。

体效应也会影响阈值电压。

小尺寸效应

实际中,随着器件沟道长度的缩小, 人们发现器件的性能开始偏离长沟道理论所预示的特性, 出现了一些不希望有的电特性。这些与长沟道特性的偏差统称为小尺寸效应, 主要的小尺寸效应有:

- 阈值电压与沟道的几何尺寸和漏极电压有关;

- 亚阈值摆幅增加, 亚阈值区和饱和区的漏极电流与漏极电压有关;

- 饱和区漏电流随栅压的变化偏离平方率关系。

因为大多数偏差与沟道长度L的减小有关,因此小尺寸效应也称为短沟道效应(SCE)。

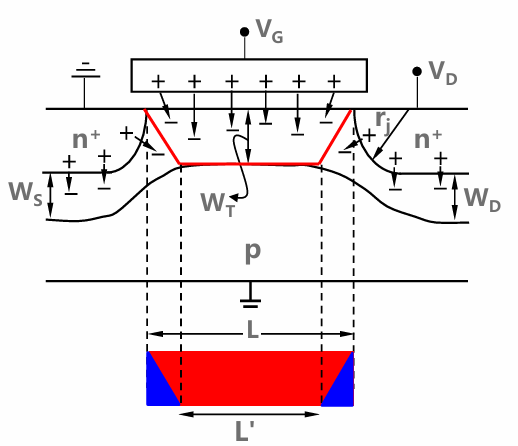

阈值电压的小尺寸效应

在\(V_{DS}\)不变时, 阈值电压随沟道长度的缩短而减小的现象称为阈值电压的滚降(\(V_T\) roll-off), 也称为阈值电压的短沟道效应。

电荷共享模型认为, 实际器件中, 栅与源、漏pn结共同分享沟道区耗尽层电荷,即源漏电荷共享。源、漏pn结分享的比例随着\(L\)的减小而增加,因而阈值电压随L的减小而减小。

要抑制源漏电荷共享,当\(L\)减小时,应减小\(r_j\),减小\(t_{ox}\),提高衬底掺杂浓度\(N_A\)。

漏致势垒降低(DIBL)

在沟道长度L不变时, 阈值电压随漏电压的增加而减小的现象叫漏致势垒降低(Drain-Induced Barrier Lowering, DIBL)。

在源区与沟道之间存在一个势垒, 此势垒阻止电子从源区进入沟道。在长沟道器件中,沟道源端势垒完全由栅压控制, 与漏压无关。在短沟道器件中,漏压使沟道源端的势垒降低,导致阈值电压随漏端电压的增加而减小,即漏致势垒降低效应。

DIBL效应对亚阈值电流的影响

由于DIBL效应,短沟道器件亚阈值电流对\(V_{DS}\)有强烈的依赖关系,亚阈值电流随\(V_{DS}\)的增加而增加,亚阈值特性向左移动。

通常测量亚阈值电流和漏偏压之间的关系检测是否发生DIBL效应。

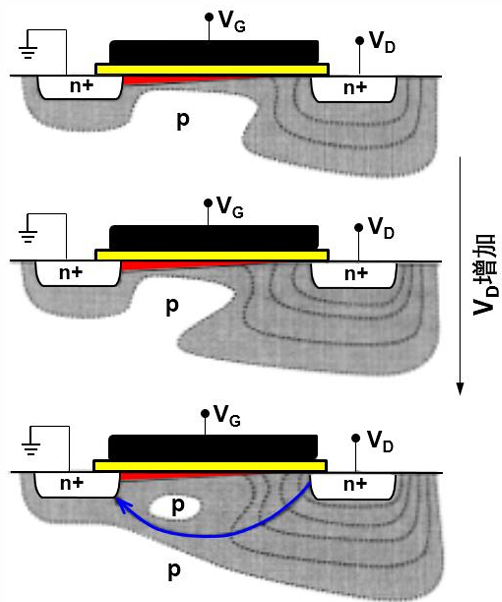

次表面穿通

次表面穿通也称为次表面DIBL效应,它发生在远离表面的衬底区。当\(V_D\)增加时,漏耗尽区在体内向源耗尽区延伸,会在体内产生一个穿通区。此后\(V_D\)稍有增加将导致穿通区源pn结的势垒降低,产生不受栅控的漏极电流。

\(V_D\)增加时漏pn结耗尽区的扩展抑制措施:提高衬底掺杂浓度,减薄栅氧厚度,减小结深,或采用新结构。

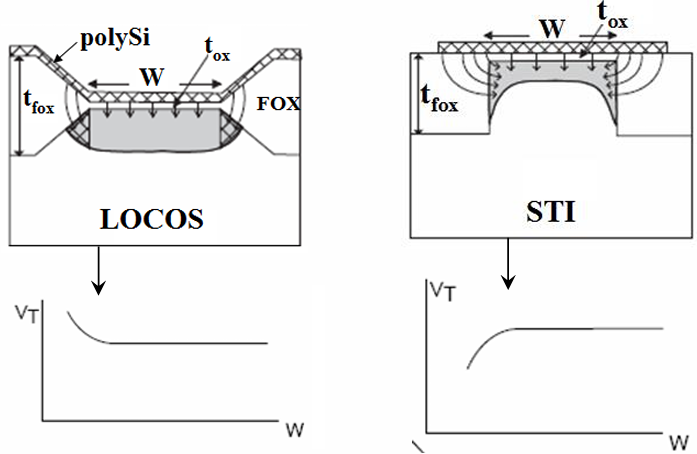

窄沟道效应

当沟道宽度较小时, 阈值电压与沟道宽度W有关, 这种现象称为窄沟道效应(Narrow Width Effects, NWE)。

表面迁移率退化和速度饱和

迁移率退化:低场迁移率随栅压的增加而减小。减小的原因:界面散射。迁移率的下降将导致MOSFET的电流和跨导降低.

弱场下载流子的漂移速度与电场呈线性关系,强场下载流子的漂移速度趋于一个极限值(该值称为饱和速度\(v_{sat}\))。速度饱和效应是指载流子的漂移速度不再随沟道方向电场的增加而线性增加且最终趋于饱和。短沟道MOSFET,需要考虑速度饱和效应。

在MOS器件中, 随着\(V_D\)的增加, 沟道中各点的电场均上升, 但电场沿沟道方向的分布是非常不均匀的, 在沟道漏端电场最大。因此当\(V_D\)增加到某个值时, 沟道漏端的电场会首先达到\(\mathscr{E}_{sat}\),从而使该处的载流子速度饱和。

定义使漏端载流子速度饱和时的\(V_{DS}\)为饱和电压\(V_{Dsat}\)。当载流子以饱和速度到达漏极时, 漏电流\(I_D\)也会饱和。

考虑速度饱和效应,饱和区电流修正为

, \(I_D\)及\(V_{Dsat}\)都小于长沟道理论的预期值;\(I_{Dsat}\)随栅压呈线性变化。

速度过冲(Velocity Overshoot)

在极小尺寸的器件中,载流子不经过一次散射就会从源运动到漏,其速度可以超过饱和速度,这种现象称为速度过冲(也称为弹道输运,Ballistic transport )

热载流子效应

沿沟道方向电场的增加将导致在沟道漏端附件出现热载流子。热载流子的危害:

- 引起碰撞电离,产生衬底电流,造成寄生BJT导通。

- 热载流子及其产生的二次电子越过硅-二氧化硅势垒,进入栅氧化层,产生界面态和栅电流。

漏压引起的饱和区的输出电导

长沟道器件饱和区电流不完全饱和的原因是沟道长度调制效应引起的, 短沟道器件饱和区电流不完全饱和

的原因如下:

- 沟道长度调制效应(\(V_{DS}\)接近\(V_{Dsat}\)的情况下)

- DIBL效应

- 热载流子效应(\(V_{DS}\)较大的情况下)

如何抑制小尺寸效应

小尺寸效应使器件工作复杂化,因此,在减小器件尺寸时,应尽可能地减小和拟制小尺寸效应,使几何上的小尺寸器件保持电学上的长沟道特性。

由于大部分小尺寸效应与沟道长度的减小有关,因此在减小沟道长度的同时,要合理地减小栅介质的厚度、沟道耗尽区的厚度和源漏pn结的结深。

按比例缩小MOSFET

恒定电场的按比例缩小理论:(k>1)

- 器件所有的横向和纵向尺寸都缩小k倍;

- 阈值电压和电源电压缩小k倍;

- 衬底掺杂浓度增加k倍;

目的是使缩小后的器件内部电场与未缩小的相同,即保持器件沟道区中电场恒定,因而称为“恒定电场按比例缩小”,也称为理想按比例缩小理论。

在实际中,理想按比例缩小理论不能被严格执行。

按经验公式设计

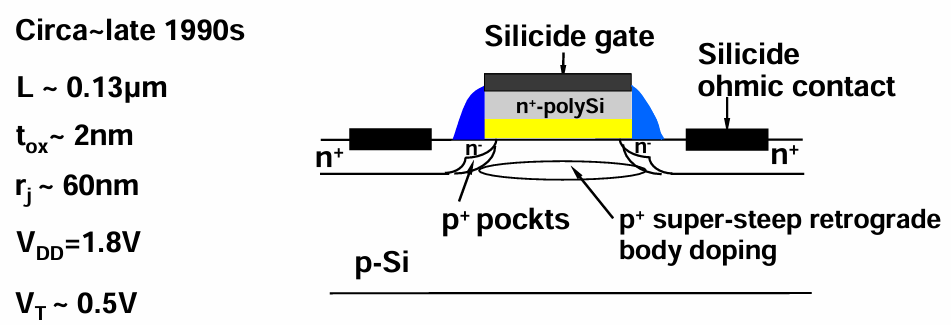

现代MOSFET 结构

Circa~late 1990s

特点: 沟道区表面轻掺杂,次表面重掺杂。\(W_{dep}\)的厚度主要由轻掺杂区的厚度决定。因此,可以通过控制轻掺杂区的厚度来降低表面耗尽层的厚度。沟道区表面轻掺杂,也提高了表面迁移率。

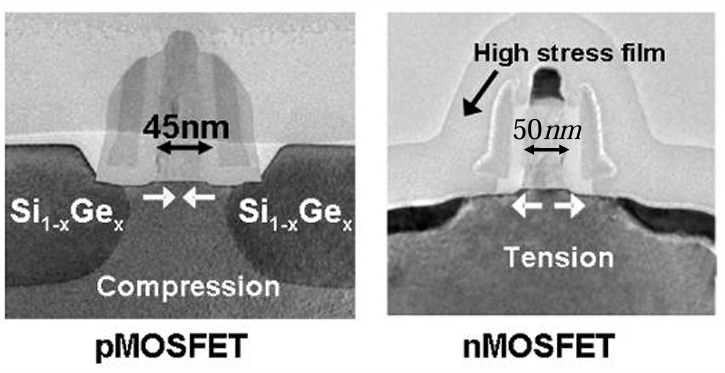

90nm Technology ~2003年

特征:采用应变硅(Strained Si)技术提高反型层载流子的迁移率。采用SiN膜覆盖nMOS,使沟道内产生张应力以提高电子的迁移率。采用SiGe源漏区对pMOS沟道产生压缩应力,以提高空穴的迁移率。

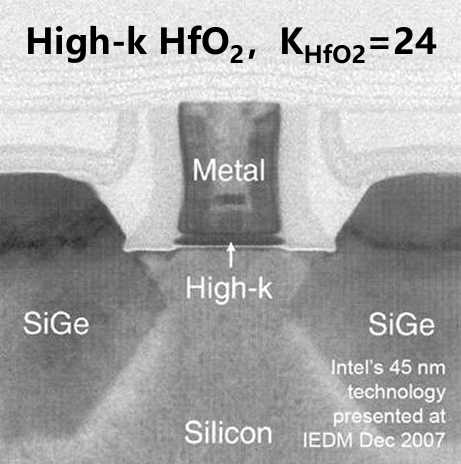

45nm Technology~2007年

特征:栅介质采用高-k介质, 栅电极采用金属(HKMG)

当栅氧薄到2~3nm以下时, 载流子会隧穿通过栅氧化层, 引起栅泄漏电流(Gate leakage)。

45nm的工艺中, 栅介质采用高-k 介质, 即通过增大栅介质的介电常数而不是减小其厚度来增大栅电容, 以避免栅介质隧穿。采用高k介质可使实际栅介质的厚度增加, 从而降低了隧穿电流。

采用金属栅(Metal Gate)的原因:消除多晶硅栅耗尽层的影响。

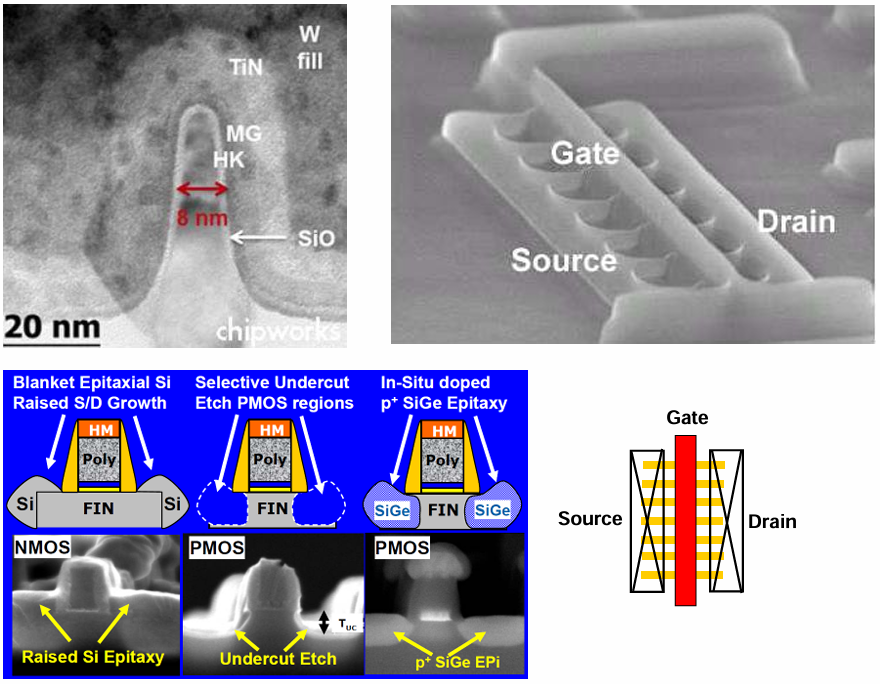

22nm Technology ~ 2012年

Multi-gate MOSFET结构的特点:栅和导电沟道不止一个;硅非常薄。与传统结构相比, 其优点:

- 栅控能力增强。由于硅膜非常薄, 很好消除了次表面穿通电流, 降低了关态电流;

- 非常薄的硅膜, 自然就减小了\(W_{dep}\)和结深, 从而抑制了\(V_T\)的下降, 因而允许\(L\)减小到几个纳米。

- 沟道不需要重掺杂来减小\(W_{dep}\), 杂质散射减小, 迁移率提高。

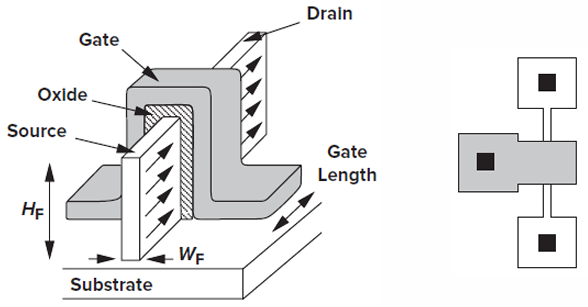

Multi-gate MOSFET的实现:FinFET

FinFET是制造在一个由硅构成的很薄的鳍状结构上, 栅极制作在鳍暴露出的三个表面上, 沟道宽度由鳍的高度和厚度决定,\(W=W_F+2H_F\)。

FinFET使得MOSFET的尺寸在传统平面晶体管尺寸极限的基础上进一步缩小。沟道长度小于5nm的FinFET已经实现。

5nm节点以后, 器件结构有可能采用围栅结构(GateAll-Around, GAA)。

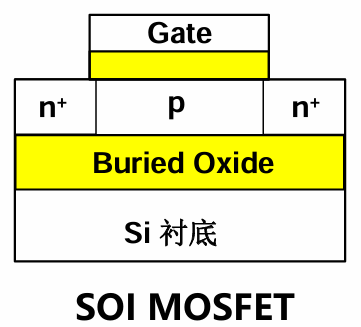

SOI MOSFET

SOI:Silicon on Insulator, 称为绝缘衬底上的硅。传统的硅晶圆称为体硅晶圆(bulk silicon)。 SOI中的绝缘层是二氧化硅或蓝宝石。现代的SOI晶圆是在硅衬底中制作一层氧化埋层, 用氧化埋层上的薄硅层制造器件。

SOI技术的优势:速度快(没有源/漏到体之间的电容), 短沟道效应小, 功耗低, 提供了制造新型结构器件的灵活性。

SOI的成本比体硅晶圆要高。

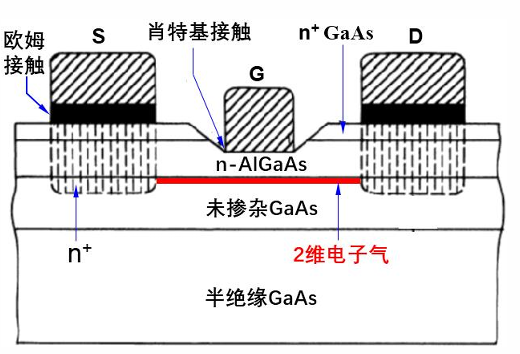

HEMT:High Electron Mobility Transistor(MOdulation Doped FET,MODFET)

掺杂的AlGaAs在不掺杂的GaAs表面产生2维电子气。HEMT栅下掺杂的AlGaAs层很薄,在平衡条件下是耗尽的,导电沟道所在的GaAs层是不掺杂的,散射最小,电子迁移率非常高且器件速度非常快。HEMT、MESFET常用于微波通讯、卫星电视接收等。

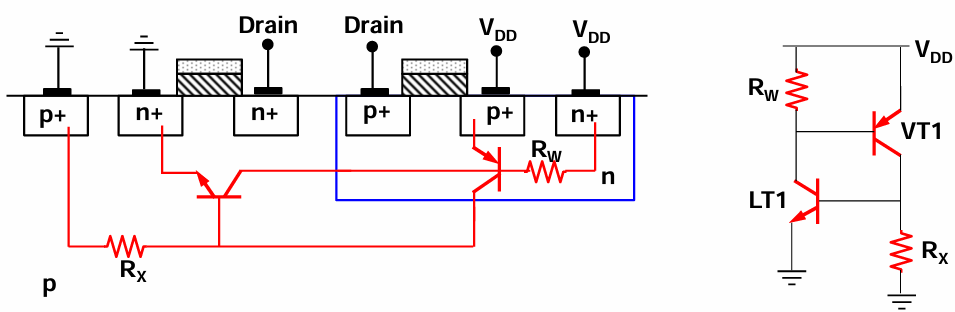

CMOS中的双极晶体管--闩锁效应(Latch-up)

闩锁效应:在一定条件下,两个寄生的BJT导通,产生从电源到地的低阻通路。

如何避免闩锁?一是将BJT的特性破坏掉。二是使两个BJT之间去耦和,防止一只双极管导通另一只。

)

![Luogu P3863 序列 题解 [ 紫 ] [ 分块 ] [ 扫描线 ]](http://pic.xiahunao.cn/Luogu P3863 序列 题解 [ 紫 ] [ 分块 ] [ 扫描线 ])