创建工程

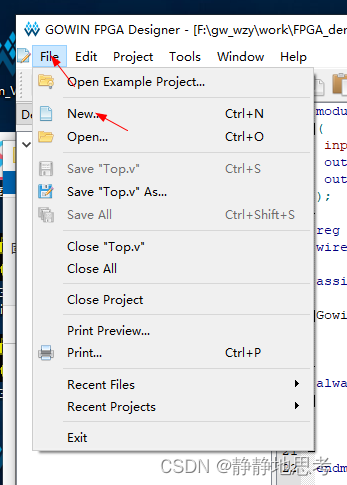

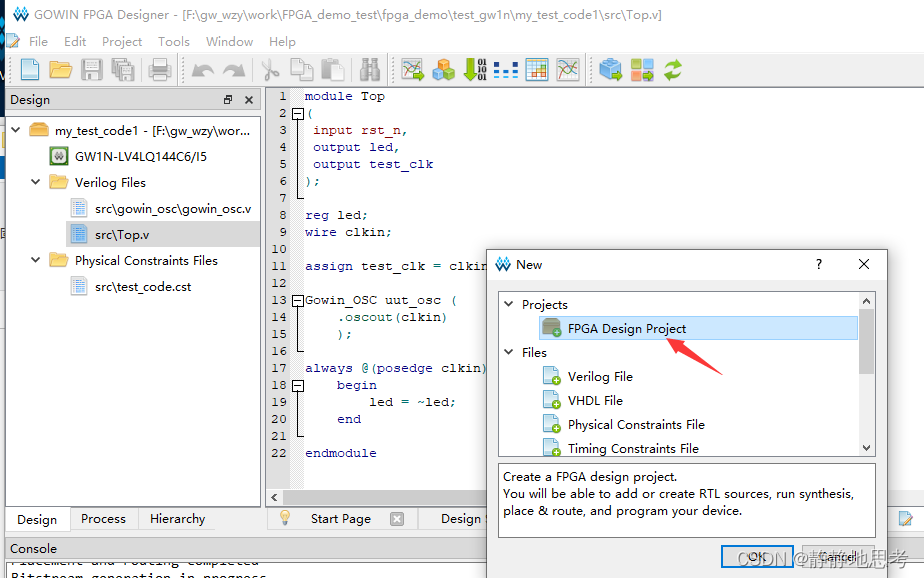

1. File 选项下,选择新建工程New..

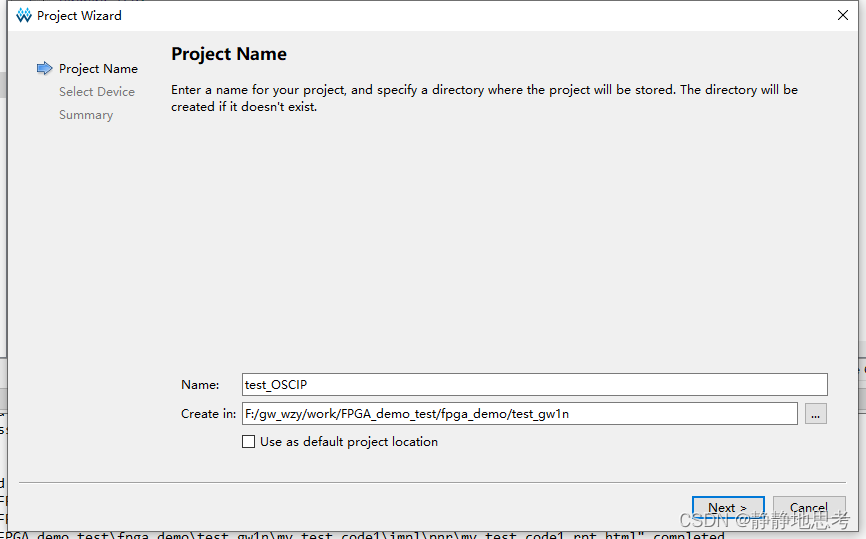

2.Name 是指工程名;Creat in 指工程路径;

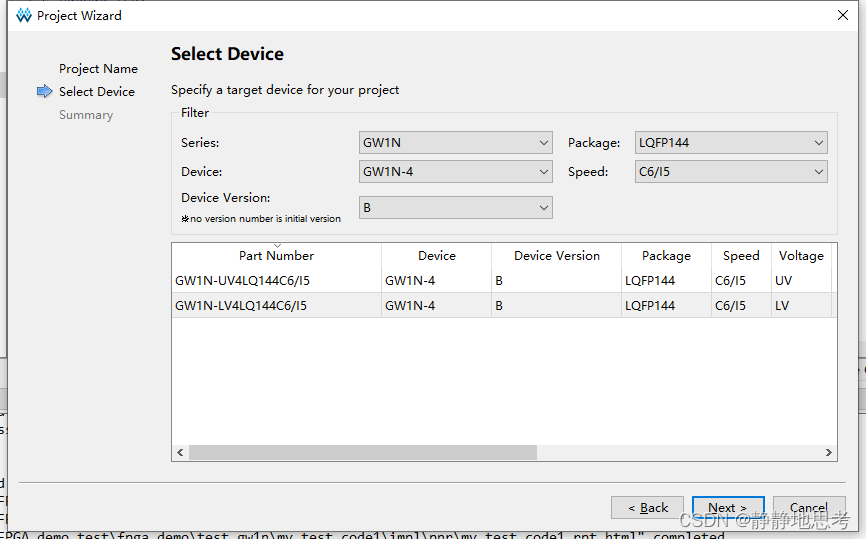

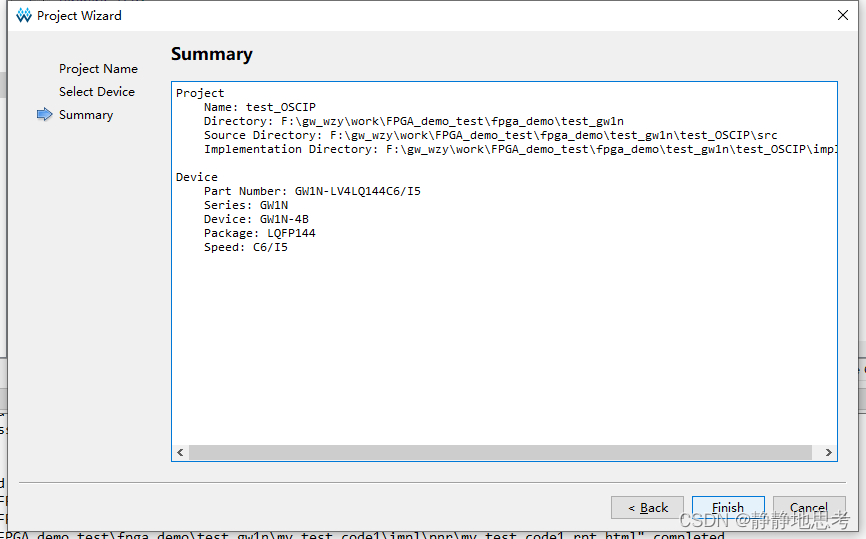

3.选择对应的 器件,本测试示例使用的是 GW1N4BLV_LQFP144C6I5;

4.选择好器件型号,单击Finish;

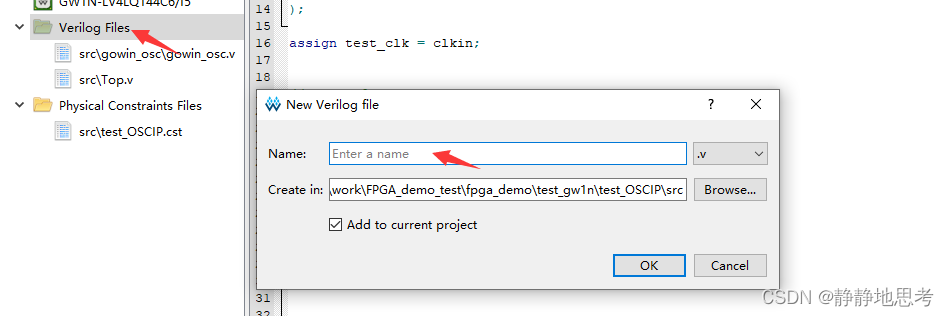

5.给工程增加VerilogFile 即 .v 文件

添加OSCIP

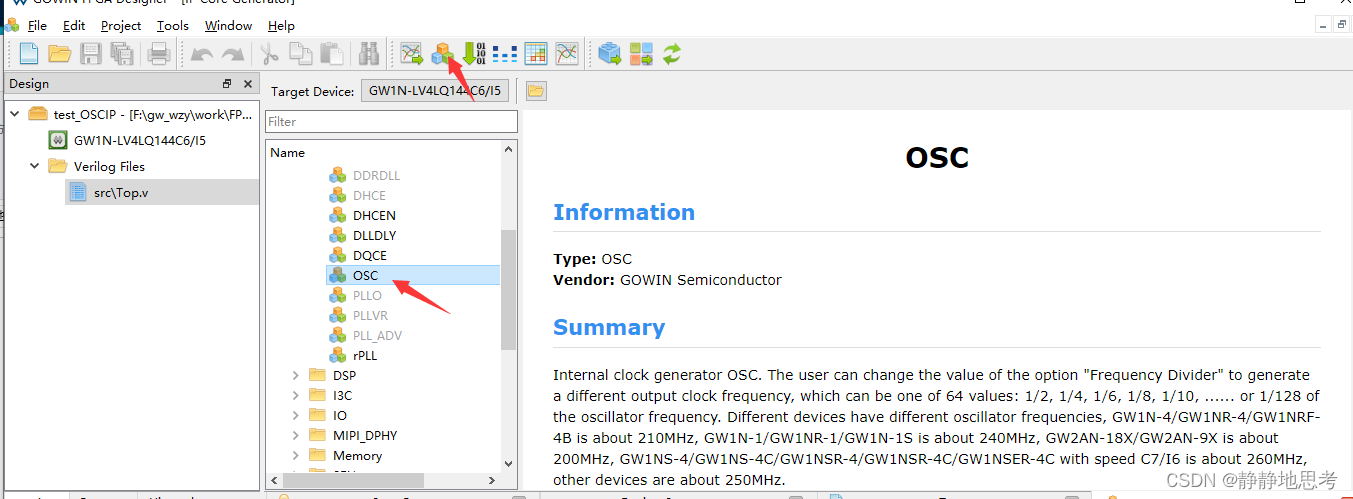

1. 单击 IP Core Generator,找到OSC IP, OSC频率默认是250Mhz,可能存在偏差;

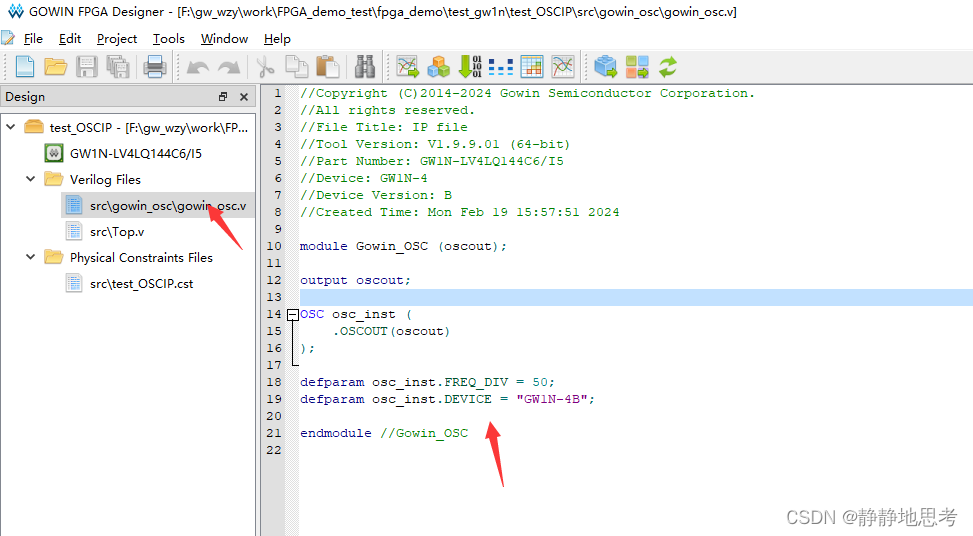

2.分频设置为50 即 250Mhz/50 =5Mhz;

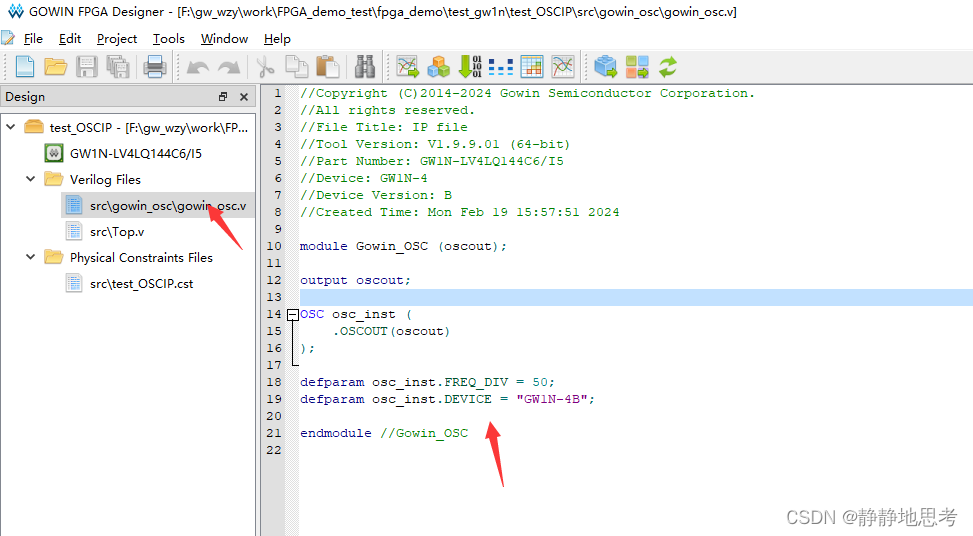

3. OSC IP 生成后 会自动添加一个 gowin_osc.v 文件

定义信号线,输出 OSC 时钟

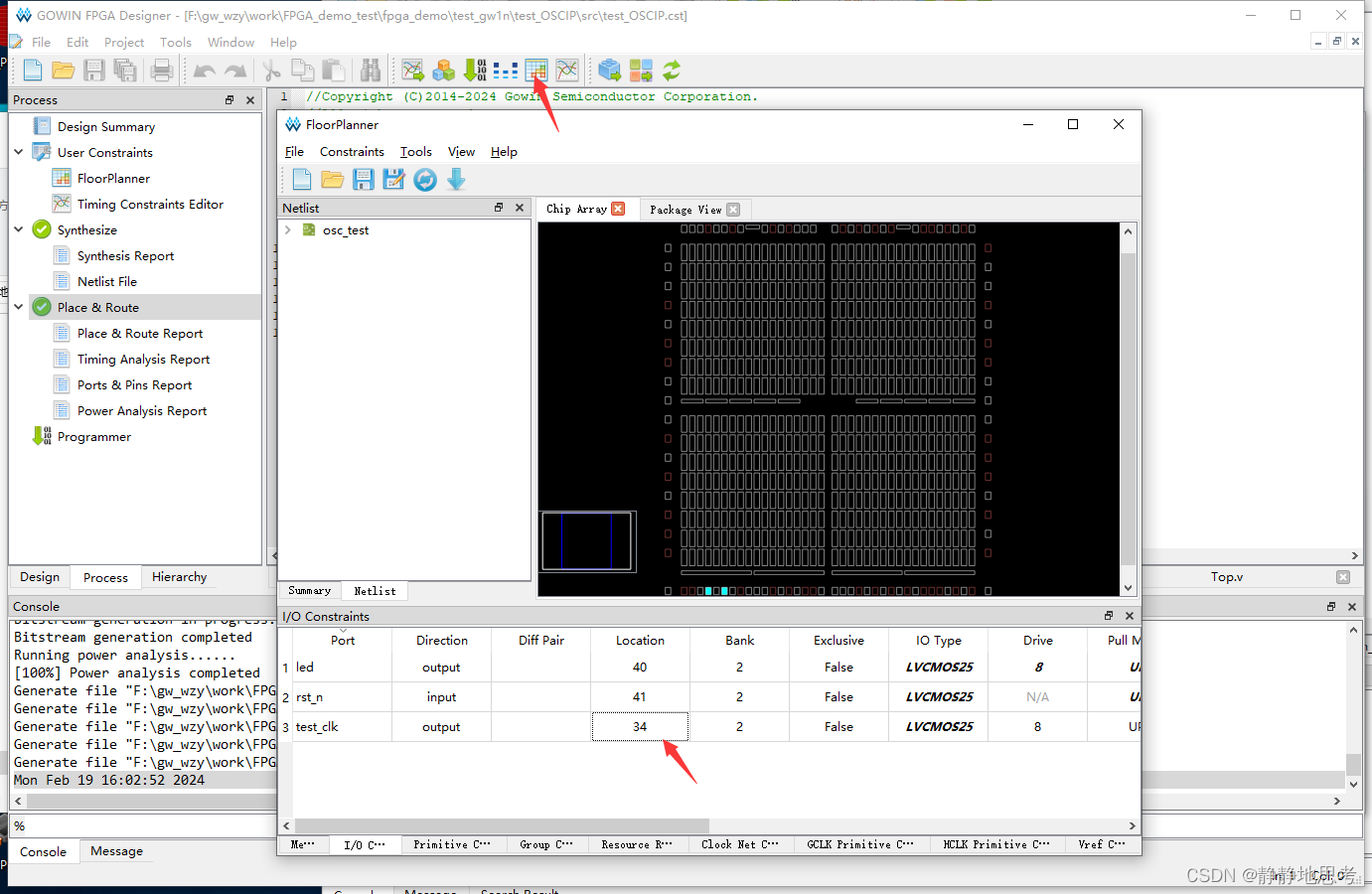

1. 单击 Floor Planner ,分配信息线到对应的引脚;

2.

定义了一个名为 Gowin_OSC 的模块,它有一个输出端口 oscout,用于输出振荡器的信号。然后,通过实例化一个名为 osc_inst 的 OSC 模块,并设置了 FREQ_DIV 和 DEVICE 的参数,将 osc_inst 的 OSCOUT 输出端口连接到 oscout。

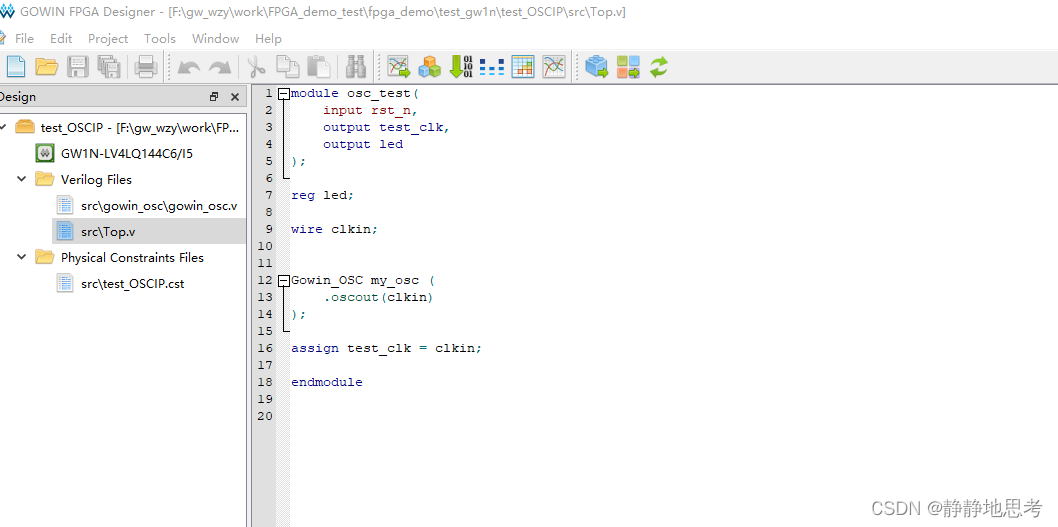

接下来,代码定义了一个 wire 类型的信号 clkin,用于接收振荡器模块输出的信号。

然后,通过实例化一个名为 my_osc 的 Gowin_OSC 模块,将 oscout 端口连接到 clkin,这样 clkin 就可以接收到振荡器模块的输出信号。

最后,使用 assign 语句将 clkin 赋值给 test_clk,这样 test_clk 就可以使用 clkin 的信号。

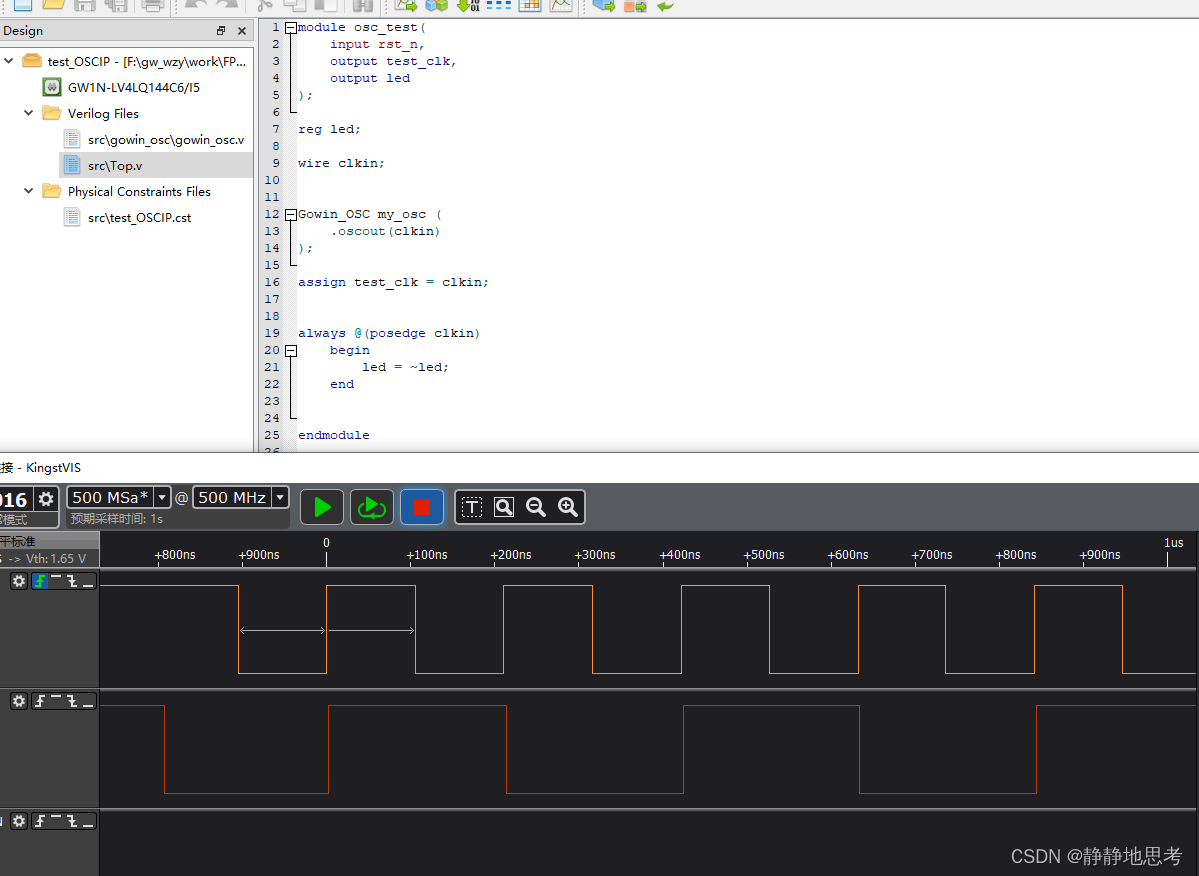

使用 OSC 时钟信号

1.clkin 信号可以输出到 test_clk ,也可以被 时序逻辑模块使用;如:使用了 always @(posedge clkin) 来表示在 clkin 的上升沿触发。也就是说,每当 clkin 信号上升沿到来时,led 的值将取反。

)

)

7系列FPGA配置引脚说明)