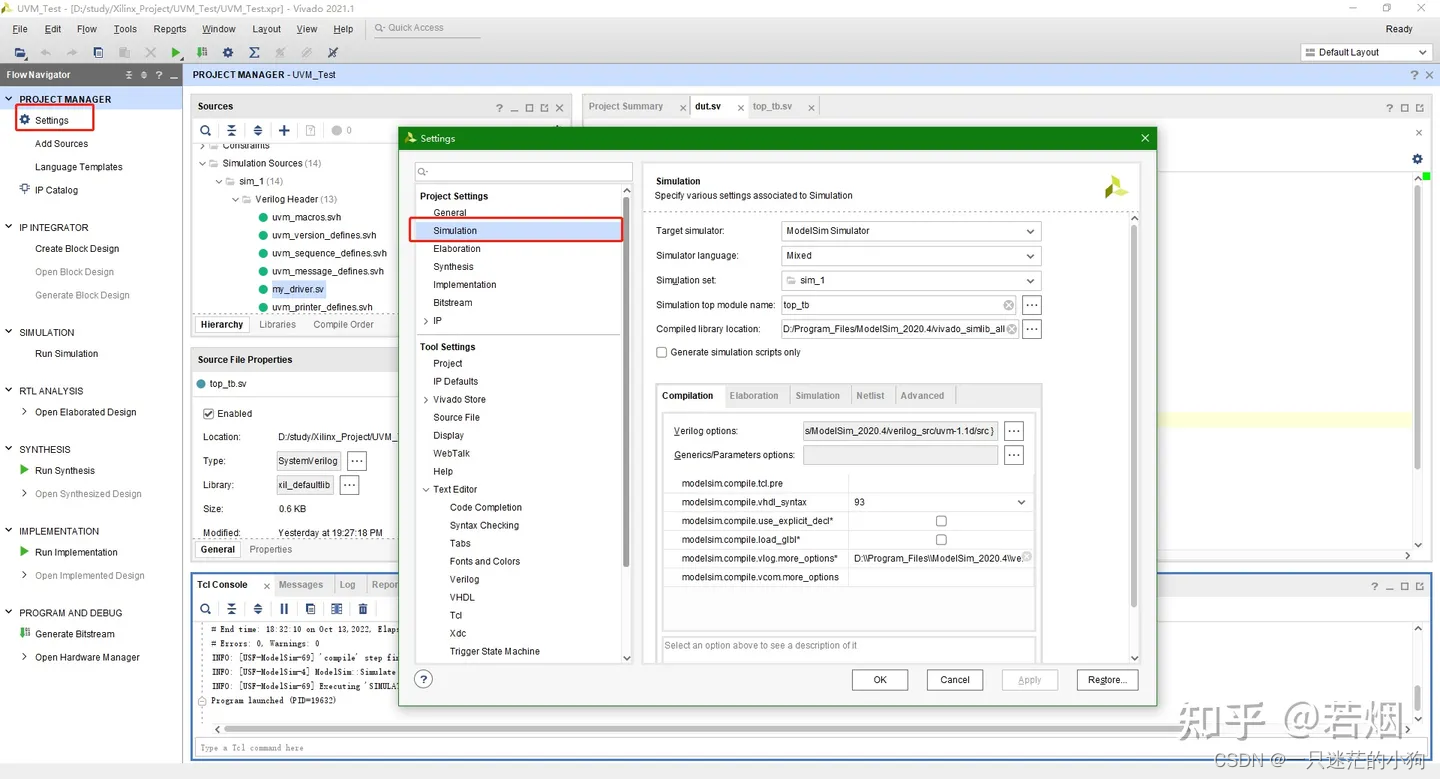

- 打开Vivado,打开对应工程,点击左侧Flow Navigator-->PROJECT MANAGER-->Settings,打开设置面板。

- 点击Project Settings-->Simulation选项卡,如下图所示。

-

将Target simulator设为Modelsim Simulator。

-

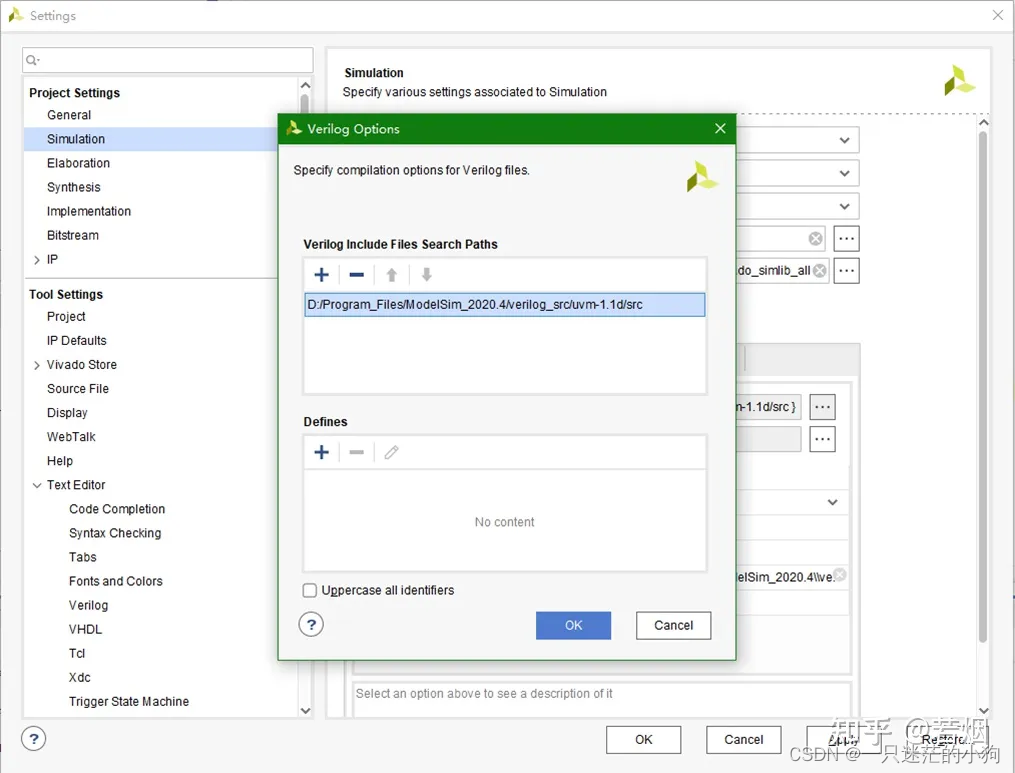

在下方的Compilation栏中,点击Verilog options右侧的…按钮,添加D:/Program_Files/ModelSim_2020.4/verilog_src/uvm-1.1d/src作为Verilog Include Files Search Paths,如下图所示。注意,D:/Program_Files/ModelSim_2020.4是我的Modelsim安装地址,Modelsim安装目录下就有对应的UVM库,这里选择verilog_src/uvm-1.1d/src。

-

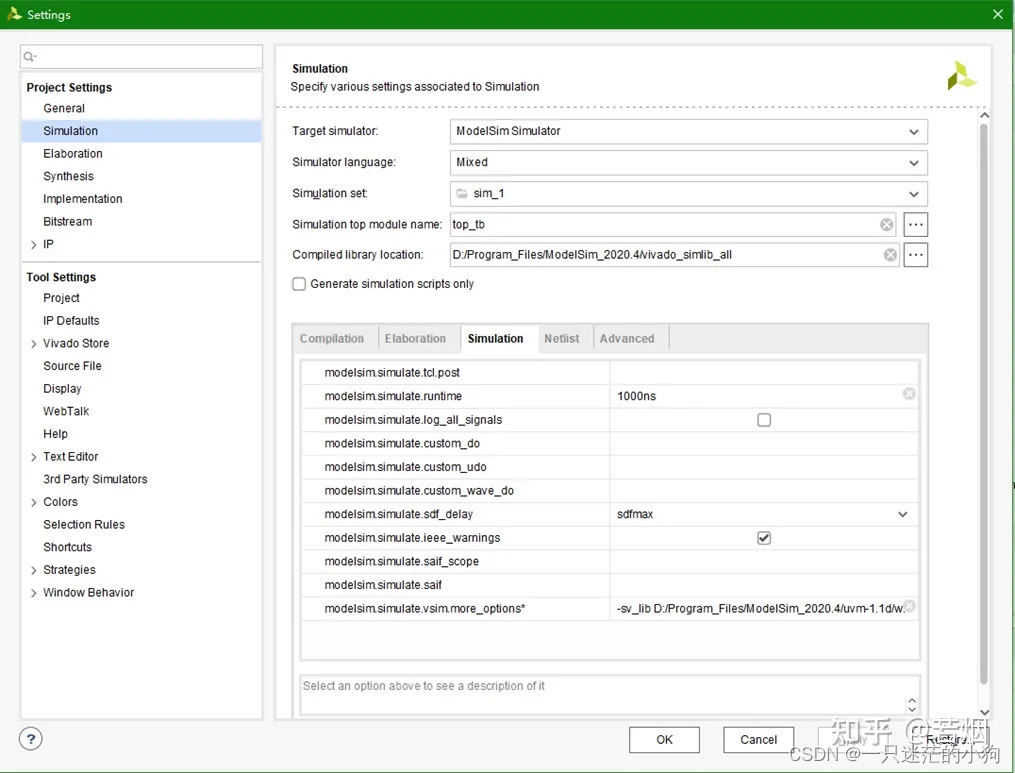

在modelsim.compile.vlog.more_options中,输入D:/Program_Files/ModelSim_2020.4/verilog_src/uvm-1.1d/src/uvm_pkg.sv。同样,D:/Program_Files/ModelSim_2020.4是我的Modelsim安装地址,Modelsim安装目录下就有verilog_src/uvm-1.1d/src/uvm_pkg.sv。

-

将Compilation栏切换为Simulation,在下方的modelsim.simulate.vsim.more_options中,输入-sv_lib D:/Program_Files/ModelSim_2020.4/uvm-1.1d/win64/uvm_dpi。,如下图所示。

-

在左上角Sources窗口中添加对应的设计文件和仿真文件,这里设计文件是dut.sv,仿真文件是top_tb.sv。

-

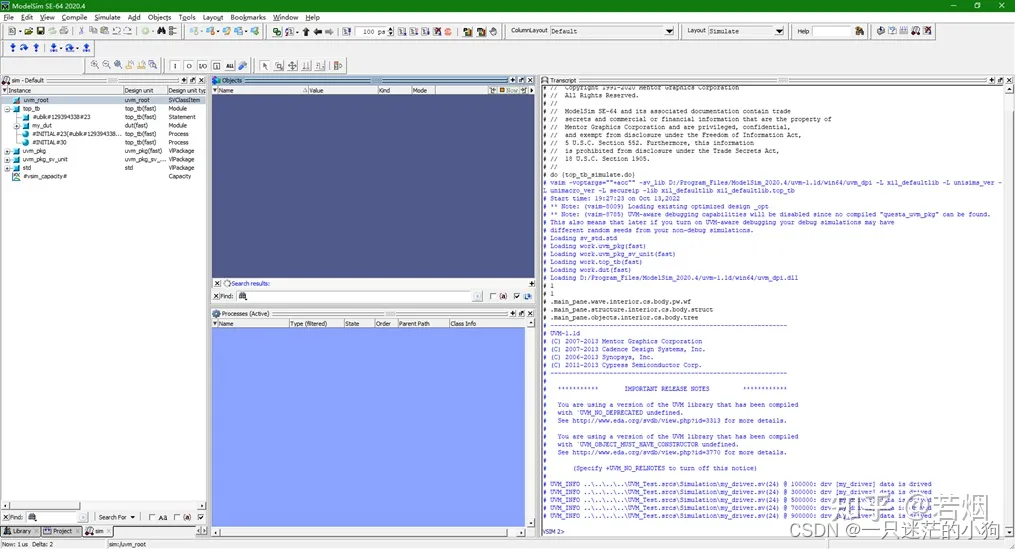

点击左侧Flow Navigator-->SIMULATION-->Run Simulation-->Run Behavior Simulation,运行行为级仿真。

-

在Modelsim的Transcript窗口中,可以看到相应输出,当然也可以查看信号波形,如下图所示。

转自:Vivado & Modelsim联合进行UVM仿真指南 - 知乎

转自:Vivado & Modelsim联合进行UVM仿真指南 - 知乎

Vivado Modelsim联合进行UVM仿真指南

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.mzph.cn/news/164530.shtml

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈email:809451989@qq.com,一经查实,立即删除!相关文章

OpenGL 绘制圆形平面(Qt)

文章目录 一、简介二、代码实现三、实现效果一、简介 这里使用一种简单的思路来生成一个圆形平面: 首先,我们需要生成一个单位圆,半径为1,法向量为(0, 0, 1),这一步我们可以使用一些函数生成圆形点集。之后,指定面片的索引生成一个圆形平面。当然这里为了后续管理起来方便…

Py之PyMuPDF:PyMuPDF的简介、安装、使用方法之详细攻略

Py之PyMuPDF:PyMuPDF的简介、安装、使用方法之详细攻略 目录

PyMuPDF的简介

PyMuPDF的安装

PyMuPDF的使用方法

1、基础用法 PyMuPDF的简介

PyMuPDF是一个高性能的Python库,用于PDF(和其他)文档的数据提取,分析,转换和操作。 …

基于JavaWeb+SSM+Vue校园水电费管理小程序系统的设计和实现

基于JavaWebSSMVue校园水电费管理小程序系统的设计和实现 源码获取入口Lun文目录前言主要技术系统设计功能截图订阅经典源码专栏Java项目精品实战案例《500套》 源码获取 源码获取入口

Lun文目录

摘 要 III Abstract 1 1 系统概述 2 1.1 概述 2 1.2课题意义 3 1.3 主要内容 3…

使用【画图】软件修改图片像素、比例和大小

打开电脑画图软件,点击开始 windows附件 画图 在画图软件里选择需要调整的照片,点击文件 打开 在弹出窗口中选择照片后点击打开 照片在画图软件中打开后,对照片进行调整。按图中顺序进行 确定后照片会根据设定的值自动调整 保存…

Codeforces Round 745 (Div. 2)(C:前缀和+滑动窗口,E:位运算加分块)

Dashboard - Codeforces Round 745 (Div. 2) - Codeforces

A:

答案就是2n!/2,

对于当前满足有k个合法下标的排列,就是一个n-k个不合法的下标的排列,

所以每一个合法排列都相反的存在一个

对称性

#include<bits/stdc.h>

using nam…

【Redisson】基于自定义注解的Redisson分布式锁实现

前言

在项目中,经常需要使用Redisson分布式锁来保证并发操作的安全性。在未引入基于注解的分布式锁之前,我们需要手动编写获取锁、判断锁、释放锁的逻辑,导致代码重复且冗长。为了简化这一过程,我们引入了基于注解的分布式锁&…

JS获取时间戳的五种方法

一、JavasCRIPT时间转时间戳

JavaScript获得时间戳的方法有五种,后四种都是通过实例化时间对象new Date() 来进一步获取当前的时间戳,JavaScript处理时间主要使用时间对象Date。

方法一:Date.now()

Date.now()可以获得当前的时间戳&#x…

快速学会使用Python3.12的新特性

一、 PEP 695: 类型形参语法的革新

PEP 695 在 Python 3.12 中引入了一种新颖且更为清晰的方式来定义泛型类和函数,旨在提升类型参数的明确性和简洁性。这个提案不仅改善了类型系统的可读性,还增强了其功能性。以下是这些变化的详细概述:

1…

(四)C语言之符号常量概述

(四)C语言之符号常量概述 一、符号常量概述 一、符号常量概述

在程序中使用像300,20等这样的等类似的“幻数”不是一个好的习惯,它们无法向阅读该程序的人提供更多有用的信息,从而使得修改程序变得困难。处理这种幻数的一种方法是…

unreal 指定windows SDK

路径 : “C:\Users\Administrator\AppData\Roaming\Unreal Engine\UnrealBuildTool\BuildConfiguration.xml”

在Configuration中添加 <WindowsPlatform><WindowsSdkVersion>10.0.20348.0</WindowsSdkVersion></WindowsPlatform>示例&…

R数据分析:集成学习方法之随机生存森林的原理和做法,实例解析

很久很久以前给大家写过决策树,非常简单明了的算法。今天给大家写随机(生存)森林,随机森林是集成了很多个决策数的集成模型。像随机森林这样将很多个基本学习器集合起来形成一个更加强大的学习器的这么一种集成思想还是非常好的。…

算法面试题:反转一个整数

题目:反转一个整数。例如,输入123,输出321;输入-456,输出-654。注意:反转后的整数在32位带符号整数范围内。

编写一个函数 reverseInteger(x: int) -> int 来实现这个功能。

答案:

def re…

【前端】必学知识ES6 1小时学会

1.ES6概述

2.let和const的认识

3.let、const、var的区别

4.模板字符串

5.函数默认参数

6.箭头函数【重点】

编辑7.对象初始化简写以及案例分析 【重点】

8.对象解构

8.对象传播操作符

9.对象传播操作符案例分析

编辑 10.数组Map

11.数组Reduce

12.NodeJS小结 …

代码随想录算法训练营第四十四天【动态规划part06】 | 完全背包、518. 零钱兑换 II、377. 组合总和 Ⅳ

完全背包

有N件物品和一个最多能背重量为W的背包。第i件物品的重量是weight[i],得到的价值是value[i] 。每件物品都有无限个(也就是可以放入背包多次),求解将哪些物品装入背包里物品价值总和最大。

题目链接:

题目页…

计算机毕业设计 基于Hadoop的物品租赁系统的设计与实现 Java实战项目 附源码+文档+视频讲解

博主介绍:✌从事软件开发10年之余,专注于Java技术领域、Python人工智能及数据挖掘、小程序项目开发和Android项目开发等。CSDN、掘金、华为云、InfoQ、阿里云等平台优质作者✌ 🍅文末获取源码联系🍅 👇🏻 精…

YOLO目标检测——泄露检测数据集下载分享【含对应voc、coco和yolo三种格式标签】

实际项目应用:泄露检测数据集说明:泄露检测数据集,真实场景的高质量图片数据,数据场景丰富,含多个类别标签说明:使用lableimg标注软件标注,标注框质量高,含voc(xml)、coco(json)和yo…

【JavaSE】不允许你不会使用String类

🎥 个人主页:深鱼~🔥收录专栏:JavaSE🌄欢迎 👍点赞✍评论⭐收藏

目录

前言:

一、常用方法

1.1 字符串构造

1.2 String对象的比较

(1)比较是否引用同一个对象

注意…

)

(C:前缀和+滑动窗口,E:位运算加分块))

C语言之符号常量概述)