下面是使用CubeMX配置STM32F407VET6,实现以太网通讯(PHY芯片为LAN8720)的具体步骤总结:

一、硬件连接方式:

-

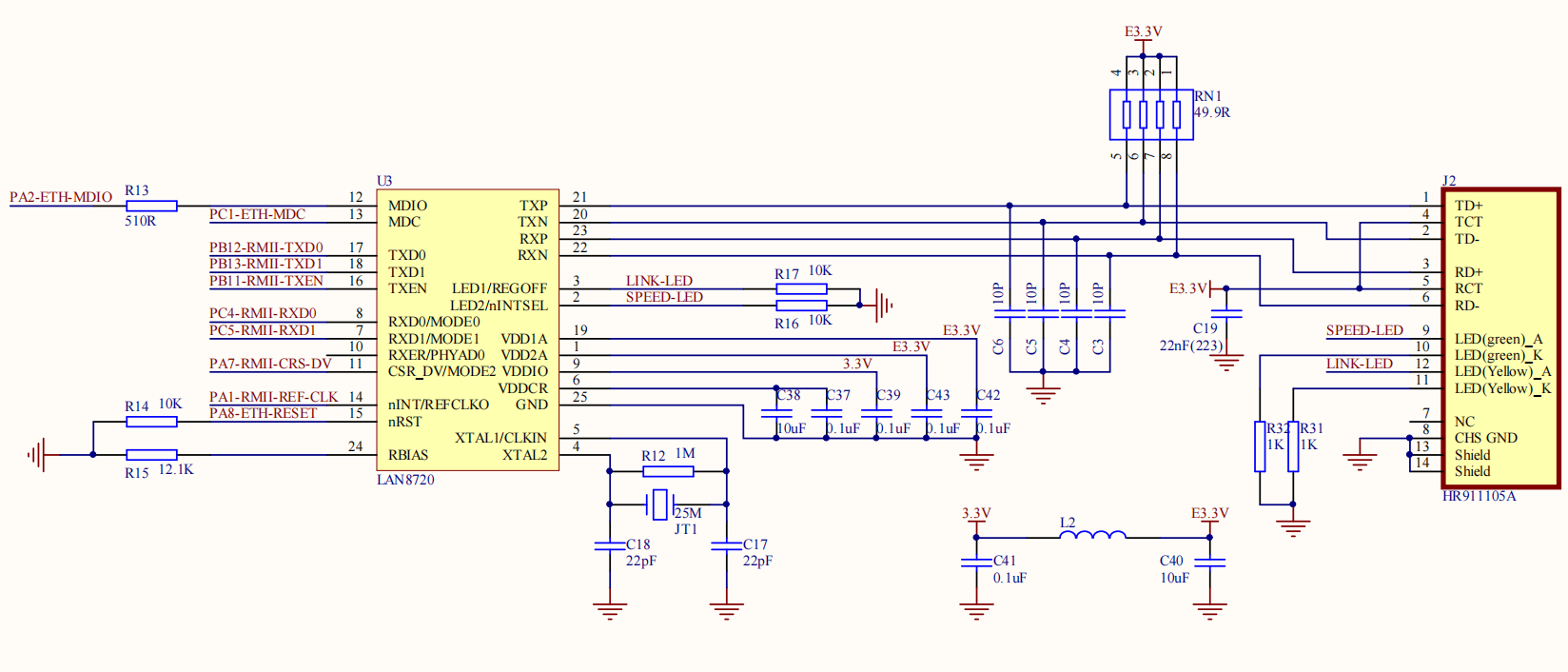

硬件原理图:

使用外部晶振为PHY芯片提供时钟。

- STM32F407VET6 与 LAN8720 采用 RMII 模式连接。

| STM32F407VET6引脚 | 功能(RMII) | LAN8720引脚 |

|---|---|---|

| PA1 | ETH_REF_CLK | REF_CLK(50MHz时钟输入) |

| PA2 | ETH_MDIO | MDIO |

| PC1 | ETH_MDC | MDC |

| PA7 | ETH_CRS_DV | CRS_DV |

| PC4 | ETH_RXD0 | RXD0 |

| PC5 | ETH_RXD1 | RXD1 |

| PB11 | ETH_TX_EN | TX_EN |

| PB12 | ETH_TXD0 | TXD0 |

| PB13 | ETH_TXD1 | TXD1 |

| PA8 | ETH_RESET | nRST |

注意:

-

LAN8720使用RMII模式,需提供50MHz外部时钟至LAN8720芯片的XTAL1/CLKIN引脚。

-

LAN8720芯片外接的晶振频率为 25MHz,连接至LAN8720的XTAL1/CLKIN管脚。

STM32F407在使用RMII模式进行以太网通信时,LAN8720内部会将这个25MHz时钟倍频为50MHz后输出到STM32的PA1引脚(ETH_REF_CLK),因此你只需要给LAN8720提供一个25MHz的晶振即可。

- 外部晶振:25MHz

- RMII参考时钟:LAN8720输出50MHz到STM32

-

-

LAN8720的地址引脚PHYAD0置0(接地),则默认PHY地址为0(我这里默认接地了,只是原理图没画出来)。

- 根据LAN8720官方Datasheet说明:

- 当PHYAD0引脚 下拉到GND 时,PHY地址为 0。

- 当PHYAD0引脚 上拉到VDDIO 时,PHY地址为 1。

在原理图中,这个引脚既未上拉也未下拉(即悬空状态),通常会导致PHY地址不确定,在实际工作中可能会导致STM32无法正确识别PHY芯片。

节点的配置)

)

笔记250407)

:进阶应用篇——Python 脚本自动化与三维可视化)

)

)

)