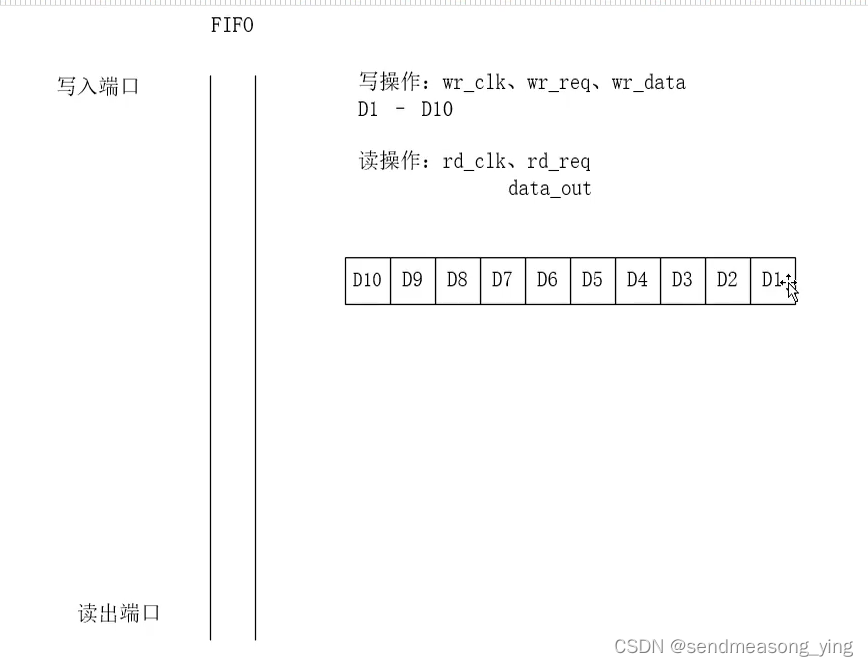

1.原理

`timescale 1ns/1ns

module tb_fifo();reg sys_clk ;

reg sys_rst_n ;

reg [7:0] pi_data ;

reg rd_req ;

reg wr_req ;

reg [2:0] cnt;wire empty ;

wire full ;

wire [7:0] po_data ;

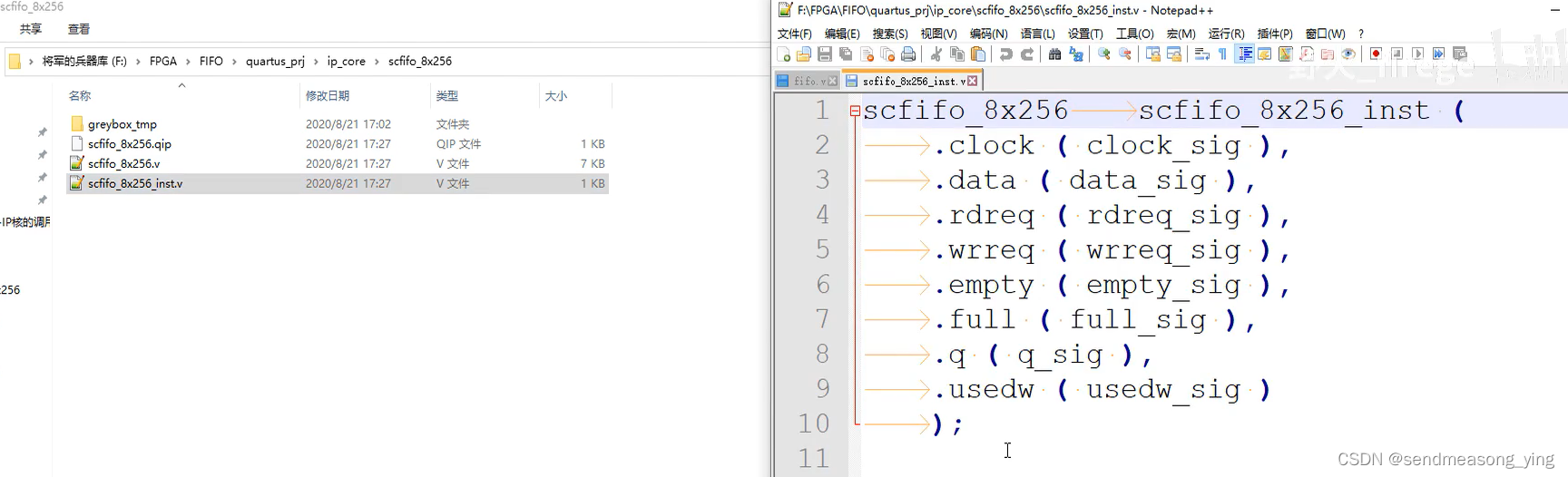

wire [7:0] usedw ;initial beginsys_clk=1'b1;sys_rst_n<=1'b0;#20sys_rst_n<=1'b1;endalways #10 sys_clk=~sys_clk;always@(posedge sys_clk or negedge sys_rst_n)if(sys_rst_n==1'b0)cnt<=3'd0;else if(cnt==2'd3)cnt<=3'd0;elsecnt<=cnt+1'b1;always@(posedge sys_clk or negedge sys_rst_n)if(sys_rst_n==1'b0)wr_req<=1'b0;else if((rd_req==1'b0)&&(cnt==3'd3))wr_req<=1'b1;elsewr_req<=1'b0;always@(posedge sys_clk or negedge sys_rst_n)if(sys_rst_n==1'b0)pi_data<=8'd0;else if((wr_req==1'b1)&&(pi_data==8'd255))pi_data<=8'd0;else if(wr_req==1'b1)pi_data<=pi_data+1'b1;elsepi_data<=pi_data;always@(posedge sys_clk or negedge sys_rst_n)if(sys_rst_n==1'b0) rd_req<=1'b0;else if(full==1'b1)rd_req<=1'b1;else if(empty==1'b1)rd_req<=1'b0;scfifo_8x256 scfifo_8x256 _inst

(.clock (sys_clk ),.data (pi_data ),.rereq (rd_req ),.wrreq (wr_req ),.empty (empty),.full (full ),.q (po_data ),.usedw (usedw )

); endmodule

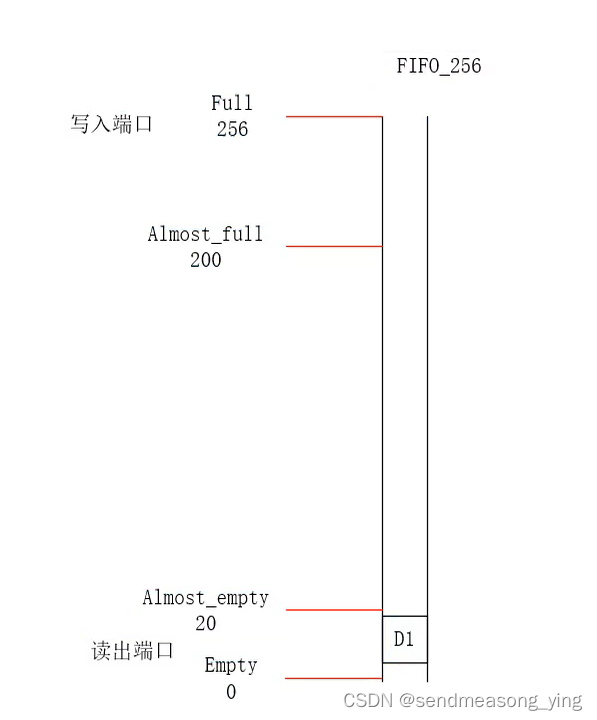

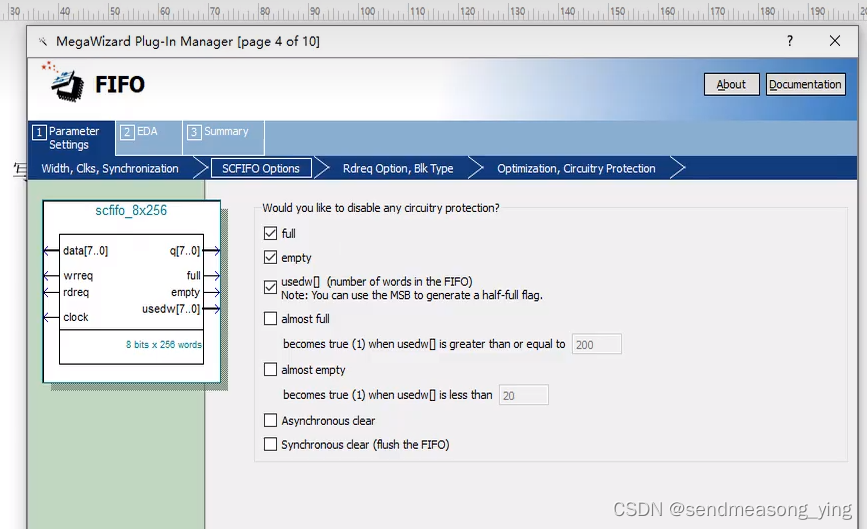

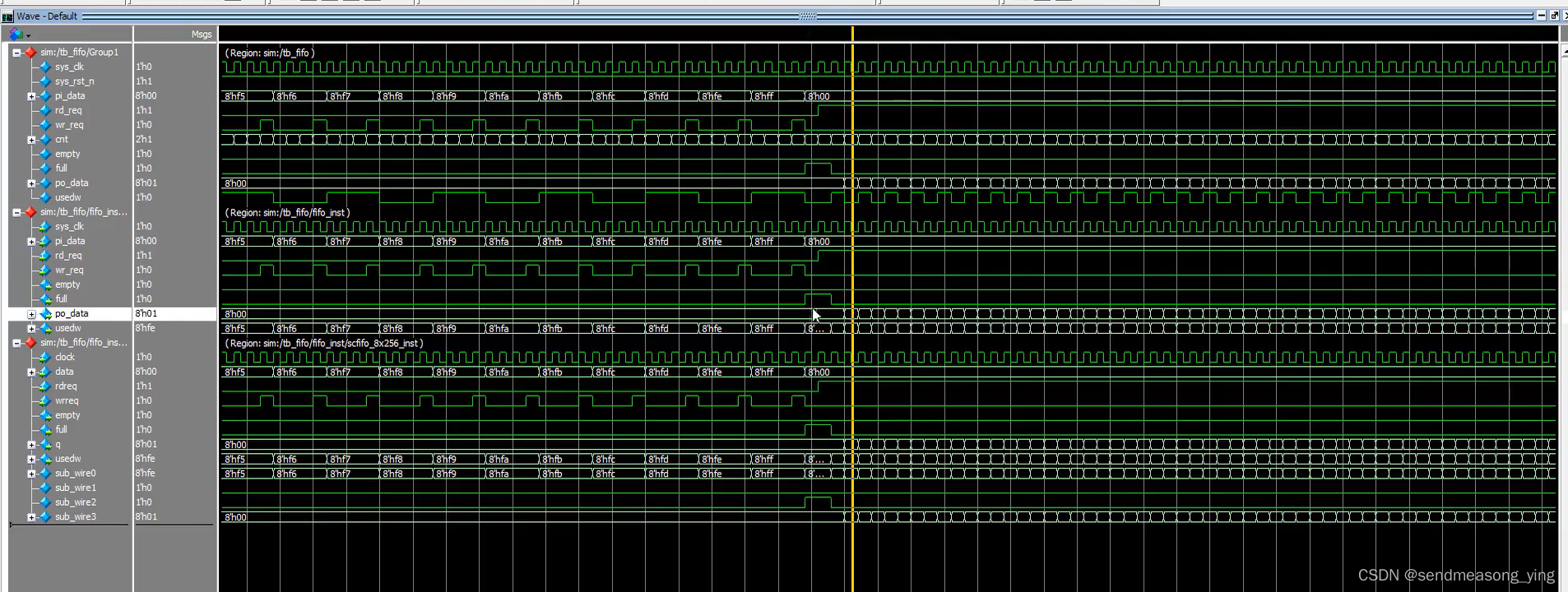

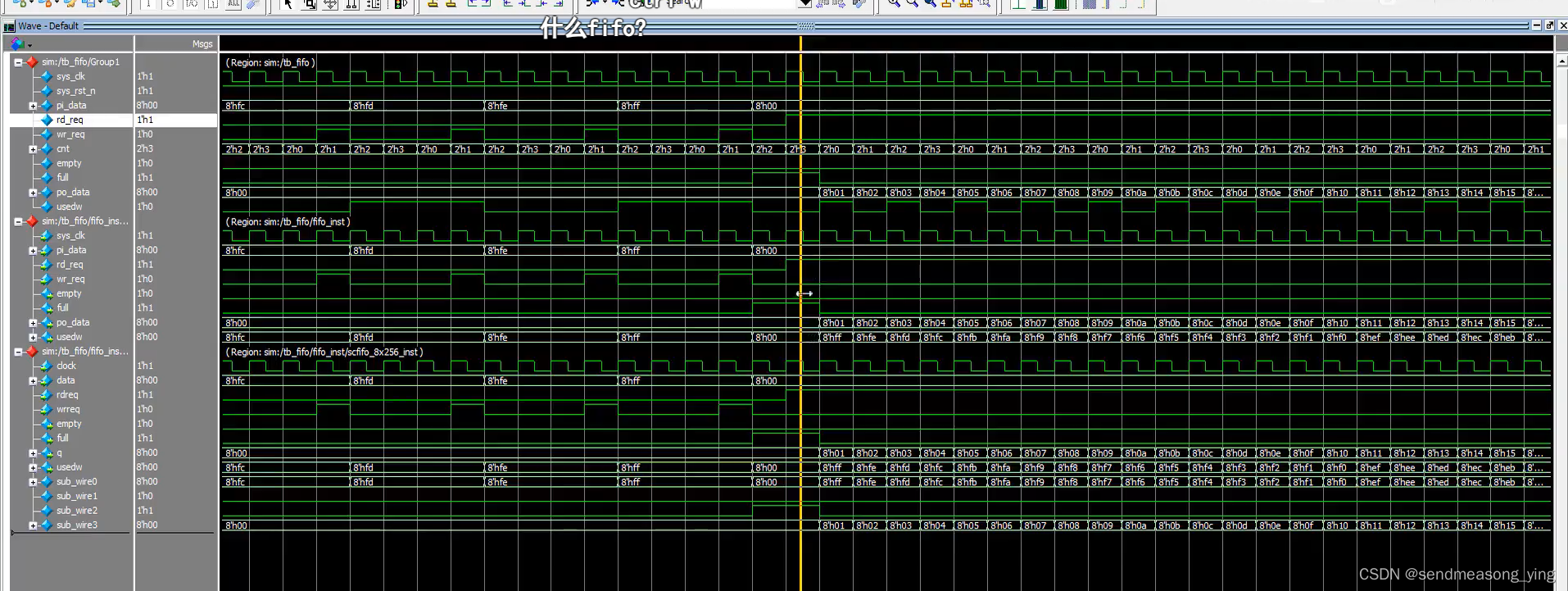

刚一写满255,此时的读请求信号还是回=会有高电平因为读请求信号要等到,写满信号为高电平时,才会在下一周期拉高,所以此时输出的数据是256,大于8位,截取的是低八位所以为0。写满255,下一个周期就拉高写满信号(时序有延时),写满信号一拉高,则rd_req就拉高表示可以读数据了,这样写请求就为低电平了。

先出fifo使能信号和数据对齐

真题C 语言 A 组-乘积尾零)

)

)

)