文章目录

- 四选一多路输出器

- verilog case 语句

- verilog 代码

- testbench 代码

- 仿真波形

- 问题小结

四选一多路输出器

制作一个四选一的多路选择器,要求输出定义上为线网类型

状态转换:

d0 00

d1 01

d2 10

d3 11

verilog case 语句

case(expression)condition1: xxx;condition2: xxx;...conditionn: xxx;default: xxx;endcase

case 的使用注意点:

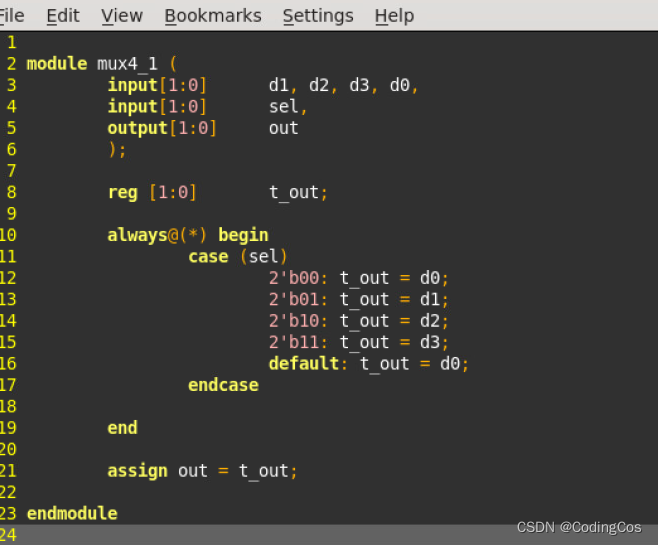

- 要在

always块里使用,如果是用always块描述组合逻辑,注意括号里的敏感变量列表都是电平触发,并且赋值时都要用阻塞赋值“=”; always块里的变量必须声明成reg类型,当然声明成reg类型不代表一定会综合成寄存器,只是语法要求always块里要这样;always块描述组合逻辑时,用*可以代表所有always块内敏感信号;- 分支条件要写全,最好补齐

default缺省条件,不然在组合逻辑中可能会由于条件不全导致出现锁存器Latch;

verilog 代码

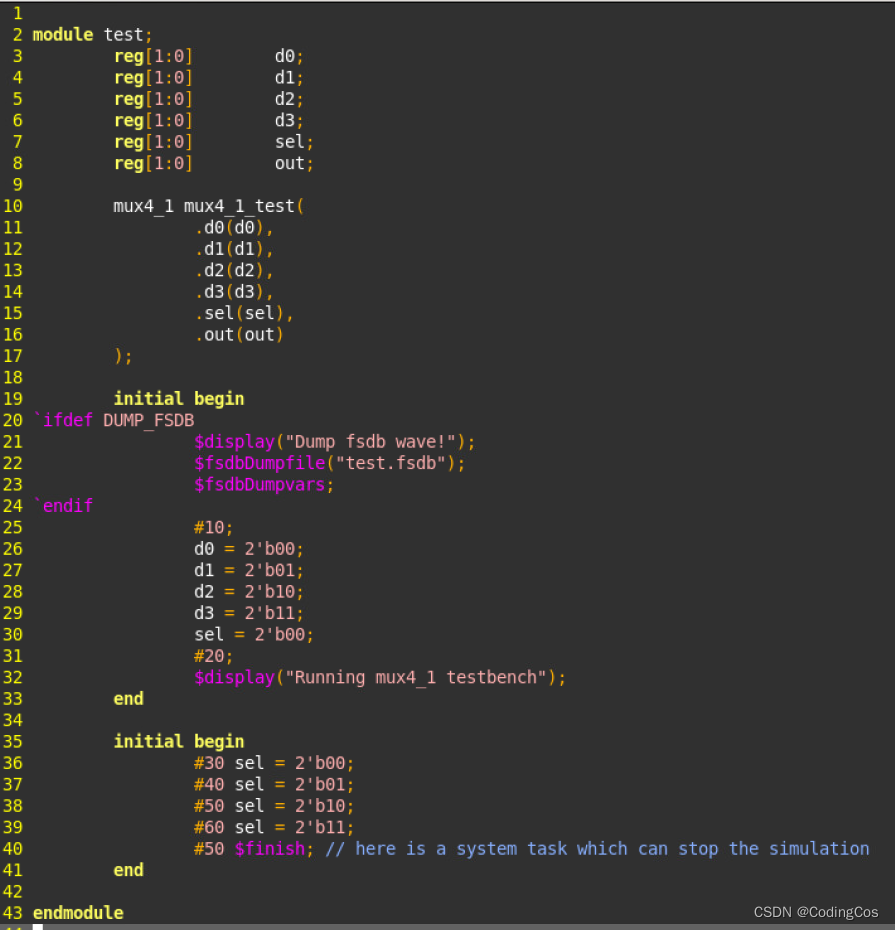

testbench 代码

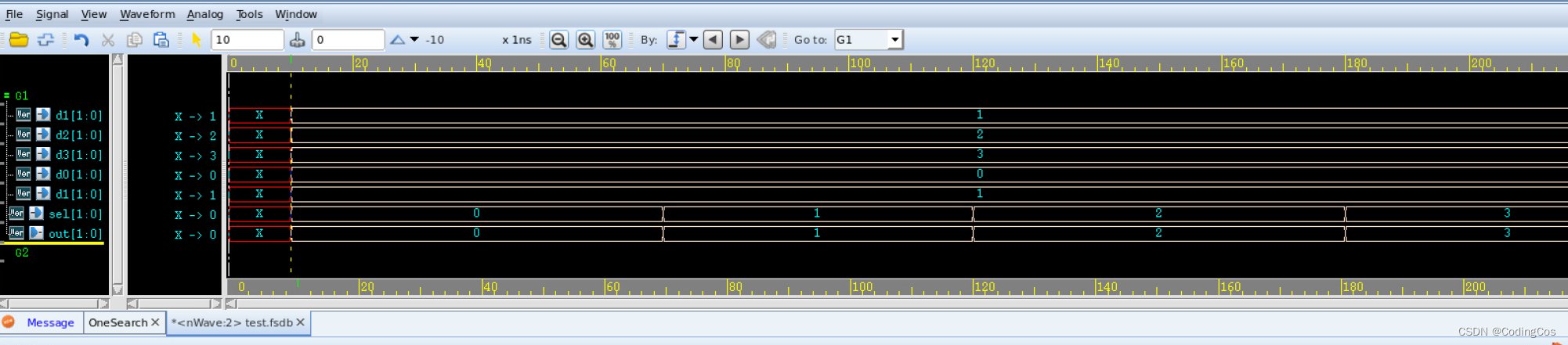

仿真波形

从波形图中可以看到 :

从波形图中可以看到 :

当sel 为 0,out 输出的值是d0;

当sel 为 1,out 输出的值是d1;

当sel 为 2,out 输出的值是d2;

当sel 为 3,out 输出的值是d3,

问题小结

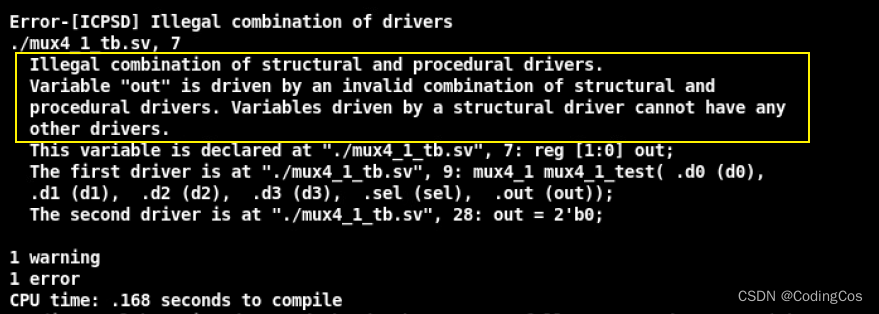

在写testbench 的时候遇到了下面问题:

问题是由于在 testbench 中对out 输出进行了赋值导致的。

推荐阅读:

https://www.bilibili.com/read/cv16177638/#reply109597547536

)

)

![[C/C++] -- JSON for Modern C++](http://pic.xiahunao.cn/[C/C++] -- JSON for Modern C++)

要对参数进行编码)