优化约束:

设置到最坏情况下会过多

布局和布线之间的关系:

最重要的是与处理器努力的,挂钩允许设计者调整处理器努力的程度

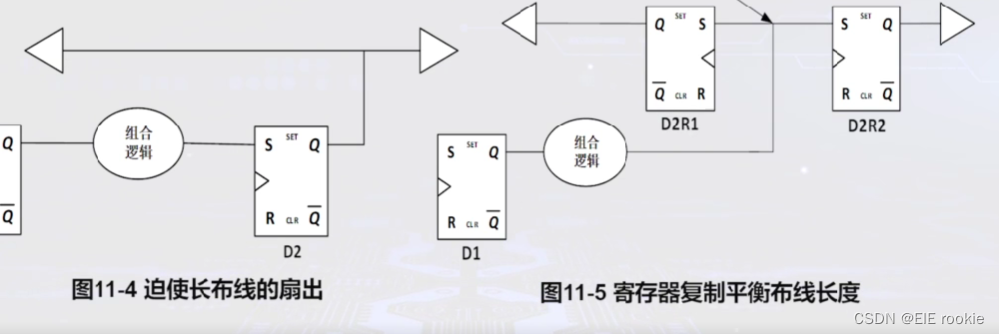

逻辑复制:

不能放置多个负载,只使用在关键路径钟

减少布线延时,但会增加面积,若不能执行这个优化,则勾选dont touch,不将其优化

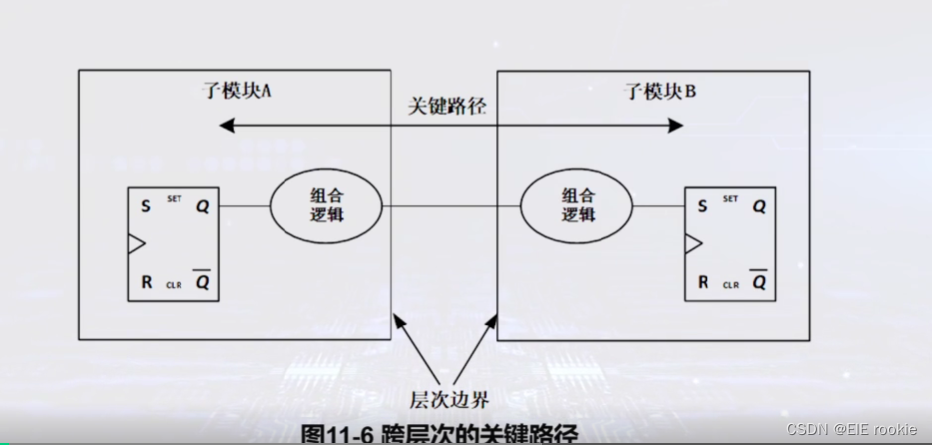

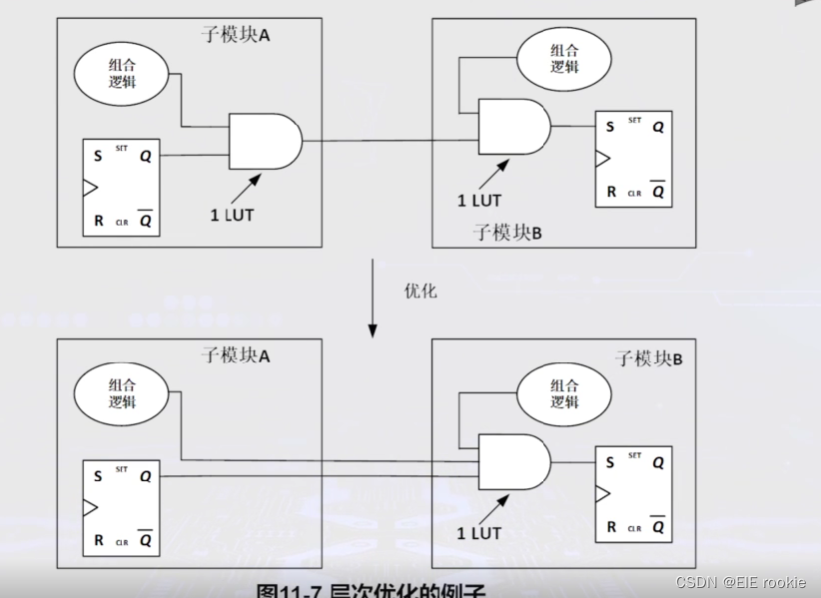

跨层次优化:

减小面积,当需要门级仿真,就不需要跨层次优化,在边界处也好调试信号

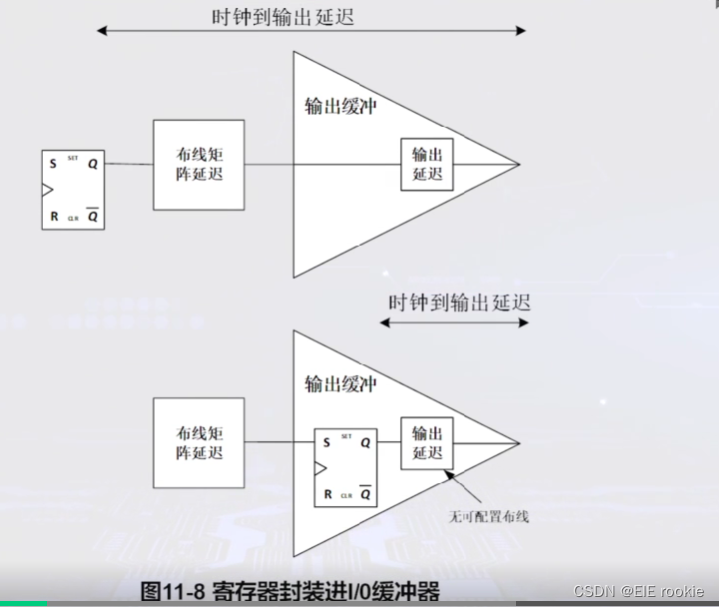

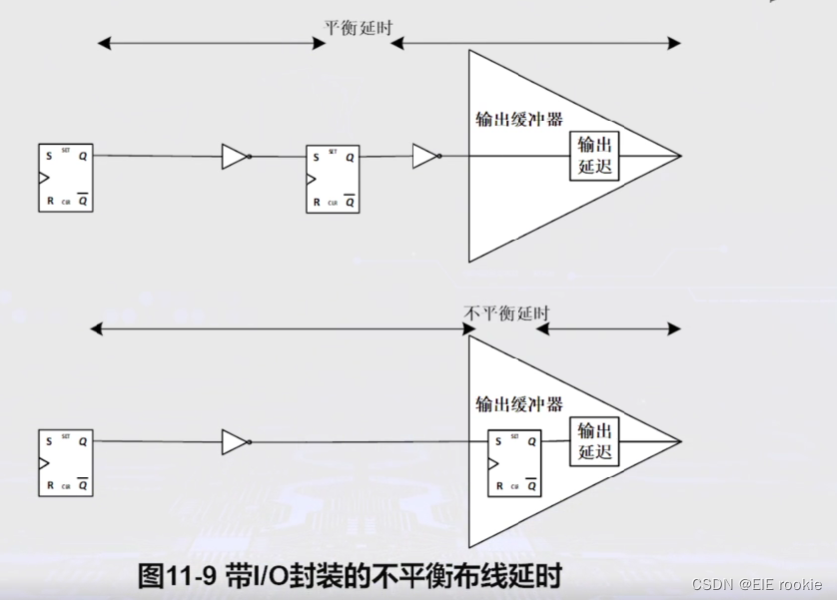

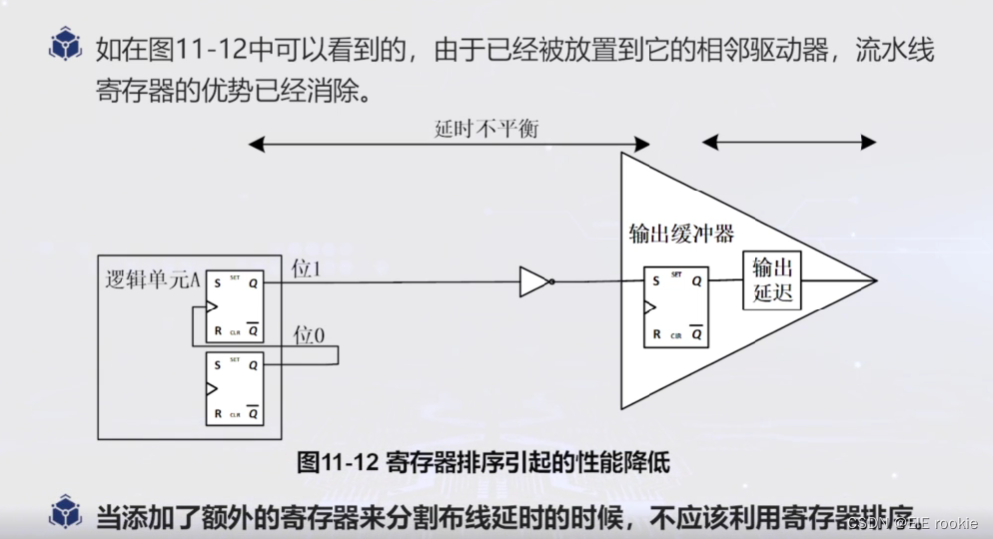

io寄存器:

时钟到输出延时就大大缩短了

不平衡延时,时序不是最优化的。

封装因子:

映射逻辑到RAM:

高端fpga是基于sram的

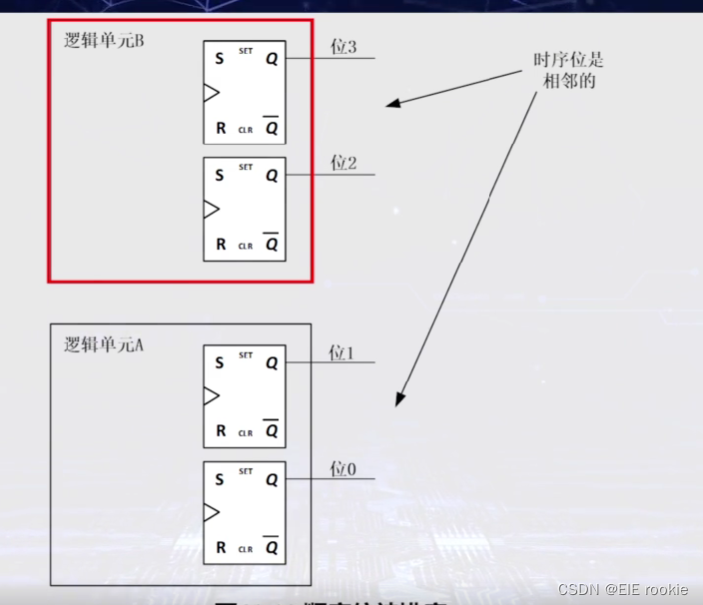

寄存器排序:

把多位寄存器的相邻位分组放进单个逻辑元件所利用的一种方式。

时序就可以被优化

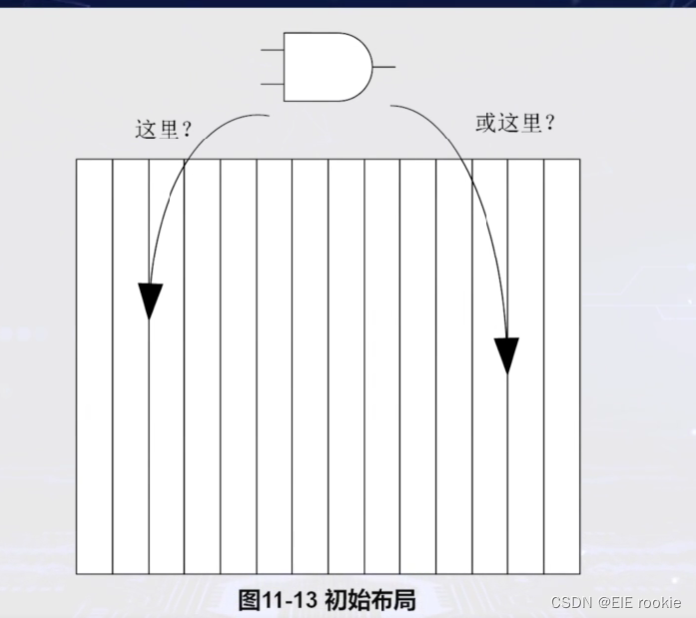

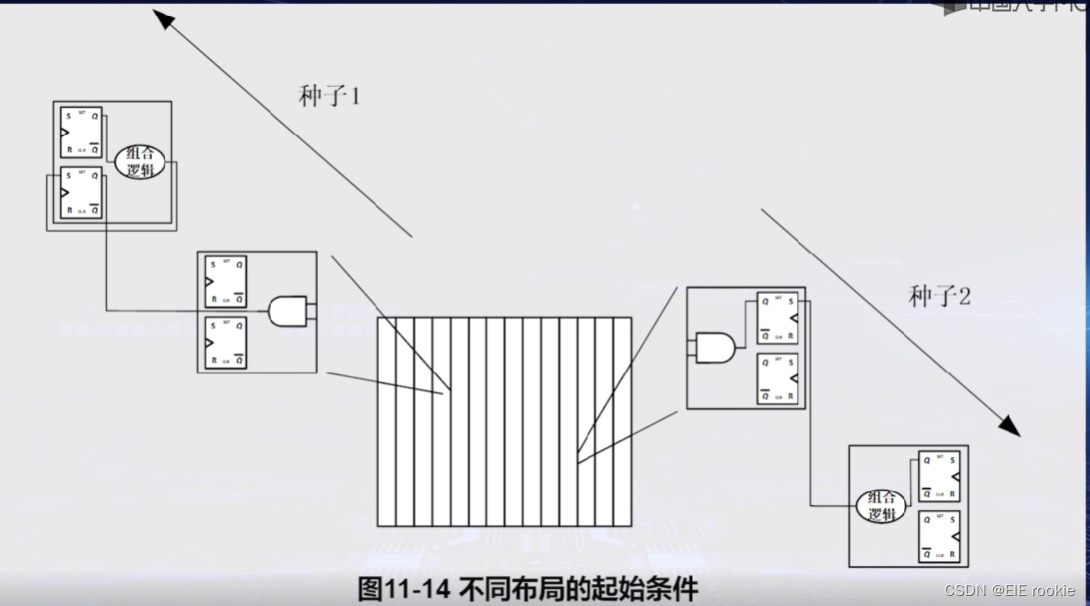

布局种子:

任何给定设计,都没有单一的最优布局。

对于自动布局器而言,确定布局过程的最佳起始点也是如此

指导布局和布线

就是找不到咋办了

)