分频时钟与使能时钟

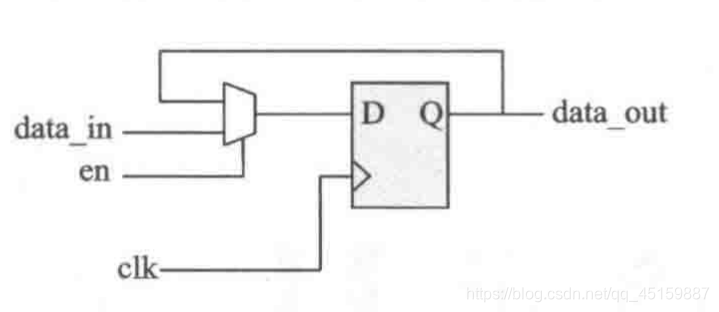

对于资源比较丰富的FPGA,一般都有内嵌的多个PLL或者DLL专门用于时钟管理,利用他们就可以很容易地达到多个时钟的设计,输出时钟能够配置成设计者期望的不同频率和相位差(相对于输入时钟),这样的时钟分频是稳定的。但是们对于某些无法使用PLL或则DLL资源的器件又该怎么办呢?推荐使用“使能时钟”进行设计,在“使能时钟”设计中只使用原有的时钟,让分频信号作为使能信号来用。

例如:设计需要得到一个50Mhz输入时钟的5分频信号即10Mhz

input clk;

input rst_n;

reg [2:0] cnt;

wire en;//5分频 计数0~4

always@(posedge clk or negedge rst_n)

beginif(!rst_n)cnt <= 3'd0;else if(cnt < 3'd4)cnt <= cnt + 1'b1;elescnt <= 3'd0;

endassign en = (cnt == 3'd4);//每5个时钟周期产生1个时钟周期高脉冲//使用使能时钟

always@(posedge clk or negedge rst_n)

beignif(!rst_n) ......;else if(en).....;

end

使能信号不直接作为时钟使用,而是作为数据输入端的选择信号,这样就避免了使用分频时钟。

欢迎关注我,关于FPGA的问题欢迎留言讨论!

函数弹出对话框)