1.)软件安装:

解压缩或执行安装文件,安装 Supra 软件。执行文件为 bin 目录中的 Supra.exe。

运行 Supra,选择菜单 File -> Import license,选择 license 文件并导入 License。

2.)新建项目:

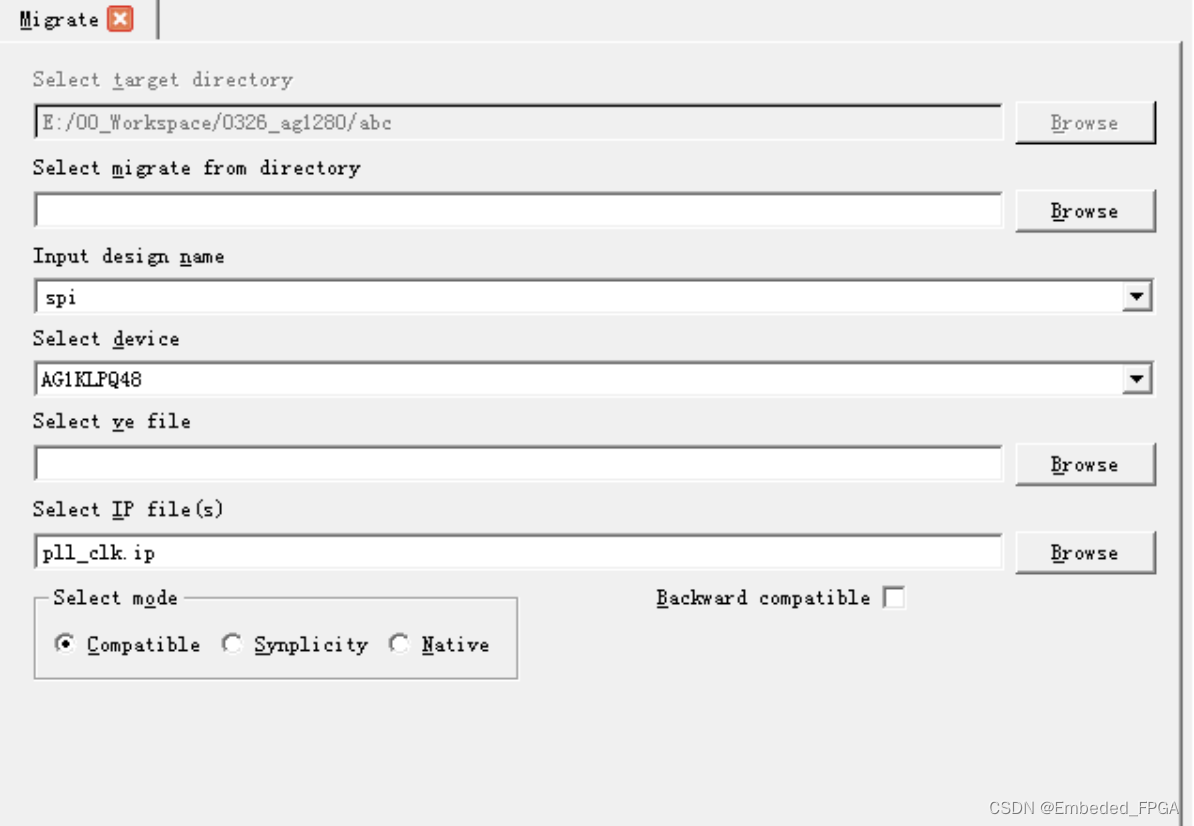

新建一工程目录。打开 Supra,进入 Tools -> Migrate:

Target Directory 选新建的工程目录,Migrate from directory 不填,输入设计名称(这里例如led),Device 选 AG1KLPQ48,ve 文件不填。

选择对应开发 Mode:Native 选项(AGM 自有 EDA 综合工具),Synplicity 选项(第三方综合工具,例如 Synplify,Mentor 等),Compatible 选项(兼容 Altera Quartus II 的综合工具)。

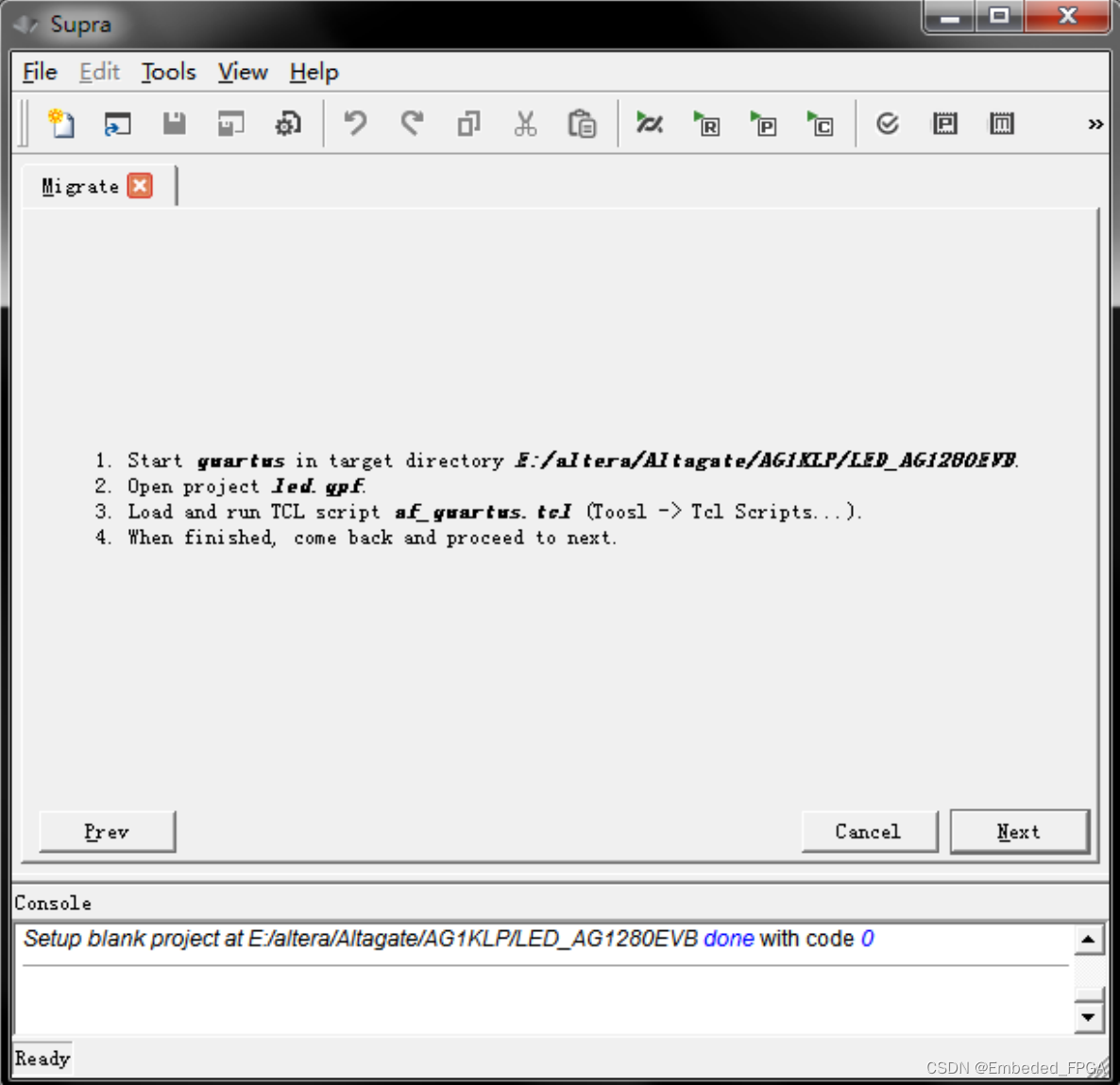

下面主要介绍 Supra 基于 Quartus II 综合的设计流程,其它工具设计流程类似。Mode 选择Compatible,点 next, 生成一个以 led 命名的 Quartus II 项目,以及空的设计文件(qpf,v,sdc 等)。

3.)项目设计:

用 Quartus II 打开 led.qpf 项目文件,修改设计文件 v,或添加其它所需设计源文件。

设计完成后,Quartus II 中选择菜单中 Tools -> Tcl Scripts…,窗口中选 af_quartus.tcl,点击 Run进行编译。

Tcl 执行过一次后,以后修改原设计,Quartus 里只需执行正常的编译(Start Compilation)。

4.)项目设置:

Quartus II 里编译成功后,编辑 DesignName.asf 文件(Supra 的设置文件,类似 Quartus II qsf文件,格式可参考 qsf 文件),

加入 IO 标准,IO 位置等设置信息,保存。

例如:set_location_assignment -to clk PIN_13

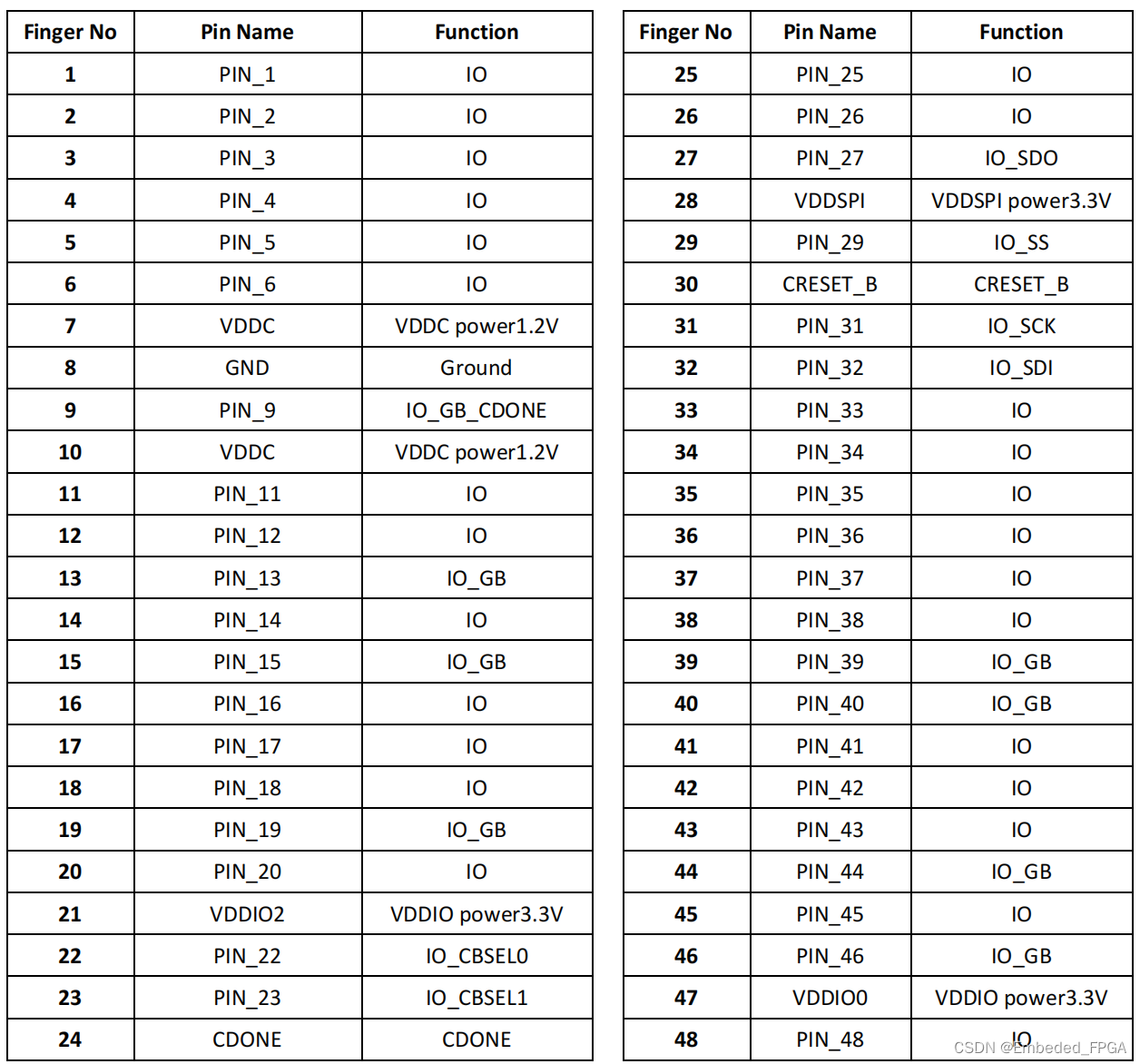

(请参考芯片的管脚映射列表,确定 IO 名称及位置)

5.)项目编译:

Supra 里继续执行 Next,开始进行编译。

编译成功后可以得到烧写文件 bin 文件。

Bin 文件为两种,led_master.bin,led .bin。分别用于 master 和 slave 的配置方式。Bin 烧写文件大小约 48K Bytes

6.)芯片配置:

Master 方式:

把 DesignName_master.bin 用编程器烧写进通用 SPI Flash 后,接入 FPGA 的 SPI 接口,实现上电即配置。

Salve 方式:

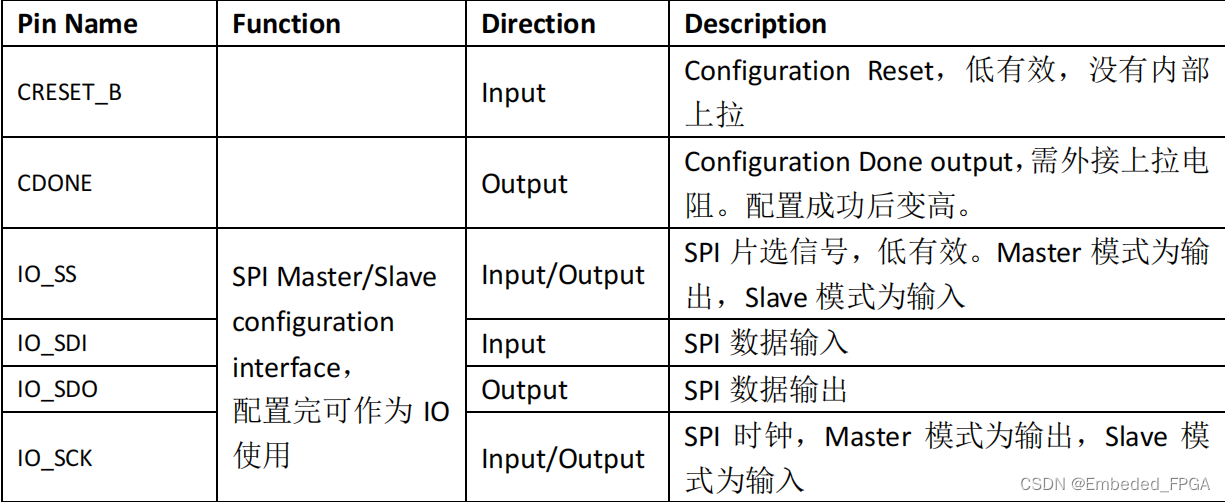

DesignName.bin 集成到外部 MCU 软件内,通过 SPI 接口把数据配置到 FPGA 内。通过 SPI 口进行 Master 或 Slave 方式配置,配置管脚说明如下:

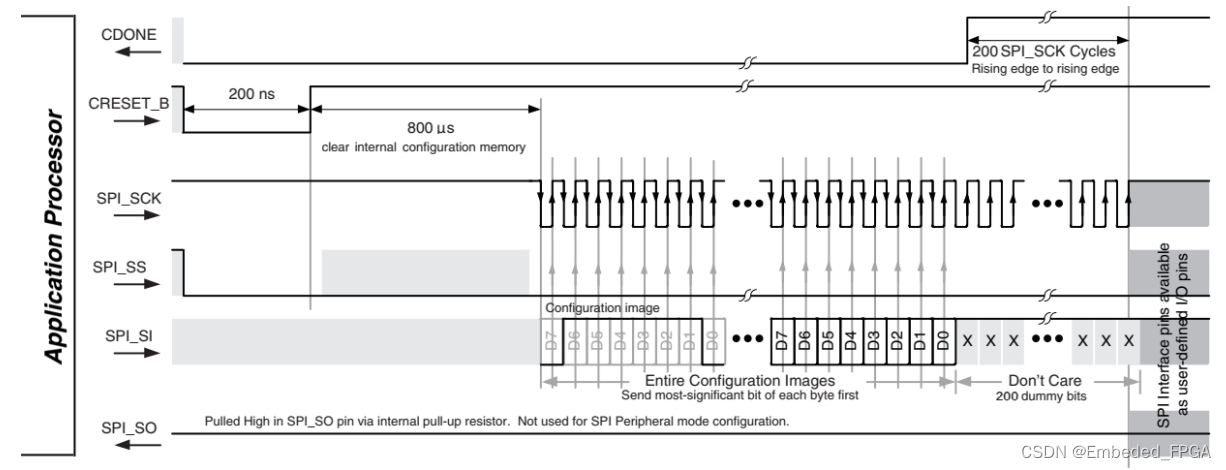

通过 MCU 配置 AG1KLP 的时序,请参考下图:

Master 配置的方式,AG1KLP 3.3V VCCIO 电源应略先于 VDDC 1.2V 上电,这样保证 FPGA 在启动前,配置 FLASH(3.3V)先启动完成,从而避免上电配置失败。

PLL 和 RAM 的使用方法

在 Supra 中进入 Tools -> Create IP,选择 PLL 或 Memory。

PLL 类型选择 PLLX,填写输入频率(MHz),输出频率,相移等数据。

注意:PLL 的输入时钟必须是芯片的全局输入时钟管脚(Pin_13,Pin_15,Pin_19 这三个)。

RAM 类型选择 BRAM,根据需要设置数据宽度和深度,以及端口方向。

完成后 Run,目录中会产生比如 pll0.v、pll0.ip 和 ram0.v、ram0.ip 两个文件。

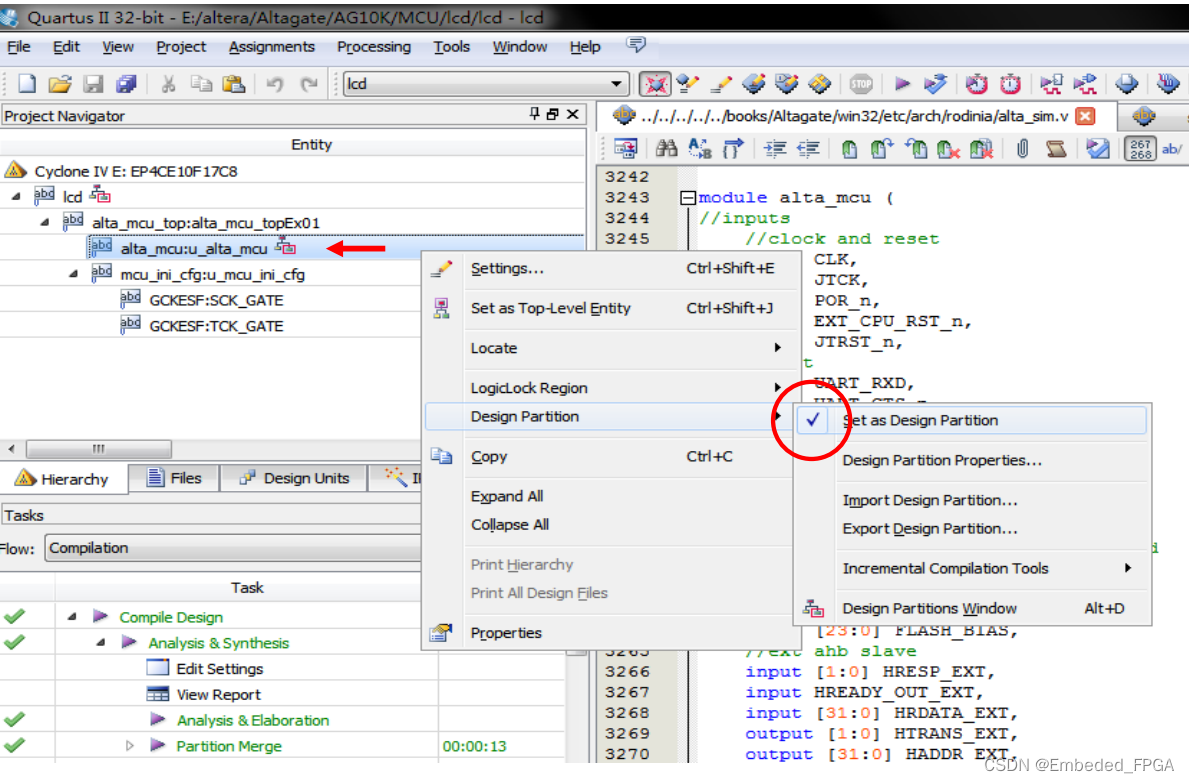

如选用 Compatible 模式,需在 Quartus II 设计中加入 IP,代码中调用产生的模块。由于 IP包 含 在 alta_sim.v 的 库 文 件 中 , 这 个 文 件 默 认 在 supra 的 安 装 目 录 中 , 如 :

C:\Supra\etc\arch\rodinia。Quartus II project 要加入这个文件,同时,要把 alta_pllx 或 alta_bram设为 Design Partition,如图:

AG1KLPQ48 Pinout

AG1KLPQ48,QFN-48 封装,body size=6mmX6mm,pitch=0.4mm

注意:全局输入信号,最好选用 IO_GB 管脚;

只有 PIN_13/15/19 可以直接接入内部 PLL;

IO_CBSEL0/1 用于多个配置数据启动,不用可忽略作普通 IO;

IO_GB_CDONE 可复用 CDONE 功能。

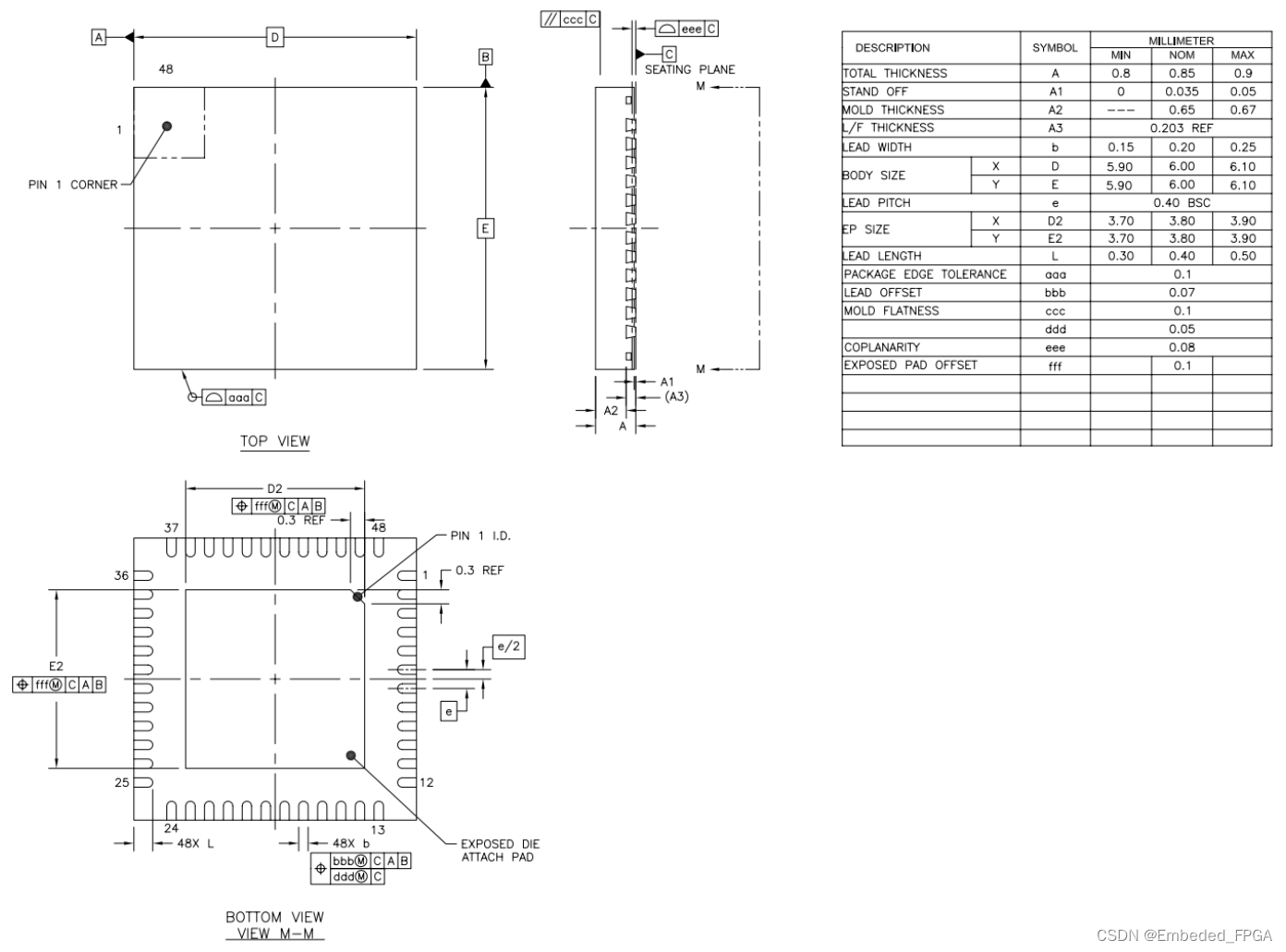

AG1KLPQ48 封装图

QFN-48 封装,body size=6mmX6mm,pitch=0.4mm

批量将横向文本改竖向)

)

)

-k8s核心对象namespace)

——js获取时间戳方法)