TIMING-4 : 时钟树上的基准时钟重新定义无效

时钟树上的时钟重新定义无效。基准时钟 <clock_name> 是在时钟 <clock_name> 下游定义的 , 并覆盖其插入延迟和/ 或波形定义。

描述

基准时钟必须在时钟树的源时钟上定义。例如 , 源时钟可能是设计的输入端口。如果在覆盖传入时钟定义的下游定义基准时钟, 时序分析准确性可能降低 , 因为它会忽略位于重新定义的基准时钟源点之前的插入延迟 , 从而导致无法正确执行偏差计算。之所以不建议这样做, 是因为这可能导致时序分析错误 , 从而导致硬件故障。

解决方案

移除下游对象上的 create_clock 约束 , 允许传输上游时钟或者创建生成时钟以引用上游基准时钟。

示例

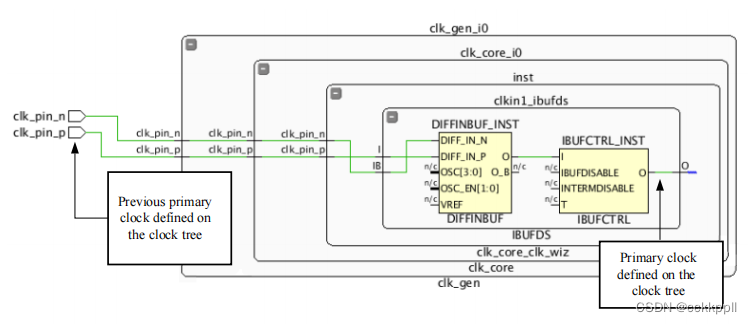

在下图中 , 在顶层端口 clk_pin_p 上已正确定义基准时钟。但 create_clock 约束用于在 IBUFCTRL 输出上重新定义基准时钟。此新时钟将忽略 IBUFCTRL 前的所有延迟。

TIMING-5 : 时钟树上的波形重定义无效

时钟树上的反向波形无效。生成时钟 <clock_name> 定义为位于时钟 <clock_name> 的下游 , 并具有波形反向定义(相比于传入时钟 ) 。

描述

应定义与传入时钟相关的生成时钟。 DRC 警告报告称生成时钟包含无效定义 , 例如 , 相比于传入时钟存在不同的周期、相移或反转。

解决方案

修改 create_generated_clock 约束以定义与传入时钟定义相匹配的正确波形定义。

示例

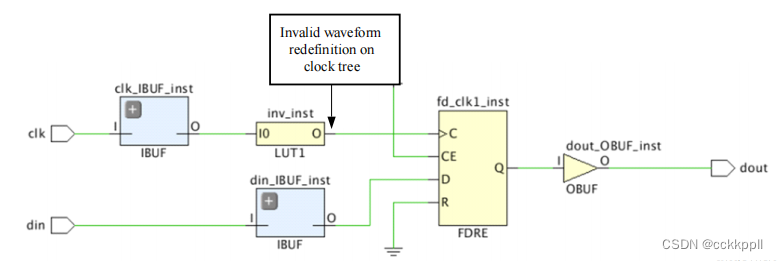

在下图中 , 在 LUT1 反相器的输出上创建了 create_generated_clock , 但未应用 -invert 开关。

TIMING-6 : 相关时钟间无公共基准时钟

时钟 <clock_name> 与 <clock_name> 之间相互关联 ( 一起定时 ), 但两者间无公共基准时钟。即使满足时序要求, 设计仍可能失败。要查找这些时钟之间的时序路径 , 请运行以下命令 :

report_timing -from [get_clocks <CLOCK_NAME1>] -to [get_clocks

<CLOCK_NAME2>]

描述

默认情况下 , 这 2 个报告的时钟被视为相关联时钟 , 并以同步方式进行定时 , 即使这 2 个时钟并非衍生自公共的基准时钟, 且不含有已知相位关系 , 也同样如此。 DRC 警告报告称时序引擎无法保证这些时钟处于同步状态。

解决方案

解决办法取决于 2 个时钟域处于异步还是同步状态。对于异步时钟 , 时序例外 ( 例如 , set_max_delay - datapath_only、 set_clock_groups 或 set_false_path ) 应覆盖 2 个域之间的路径。当这 2 个域之间的所有路径都实现例外完全覆盖时, 即可解决 DRC 。

示例

对于同步时钟 , 如果原先 2 个时钟具有相同波形 , 那么可在 2 个时钟源对象上定义同一个时序时钟 ( 请参阅以下示例) 。

示例 1 : create_clock -period 10 -name clk1 [get_ports <clock-1-source> <clock-2-

source>] 如果 2 个时钟波形不同 , 那么可将第 1 个时钟定义为基准时钟 (primary clock) , 将第 2 个时钟定义为生成时钟 (generated clock), 并将第 1 个时钟指定为主时钟 (master clock) ( 请参阅以下示例 2 ) 。

示例 2 : create_clock -period 10 -name clk1 [get_ports <clock-1-source>]

如果时钟相关联 , 但时钟周期比率为 2 , 那么解决方案是在 1 个时钟源上创建基准时钟 , 而在第 2 个时钟源上创建生成时钟:

create_generated_clock -source [get_ports <clock-1-source>] -name clk2 -divide_by 2

[get_ports <clock-2-source>]

)

)