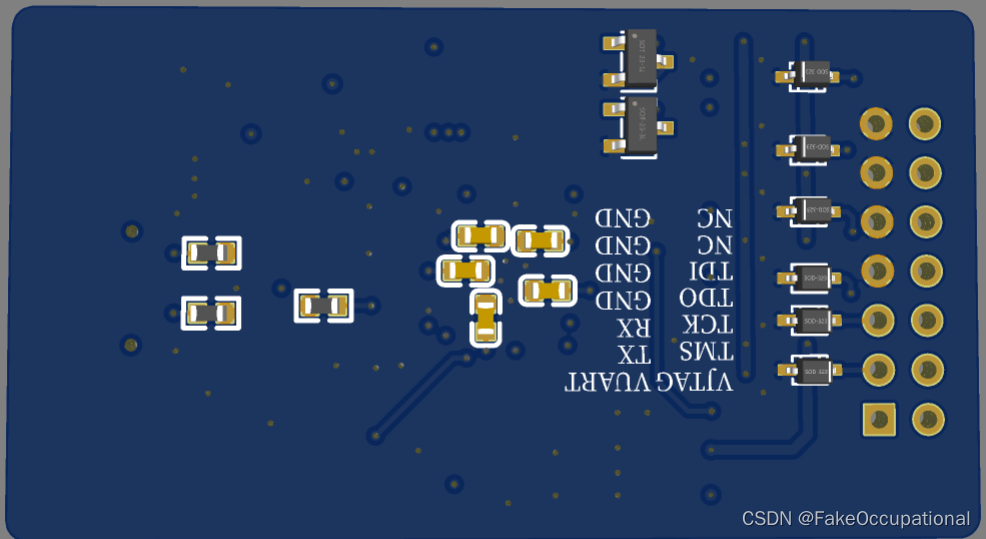

JTAG接口说明

- JTAG 接口根据需求可以选择20针或14针的配置,具体选择取决于应用场景和需要连接的功能。比如之前的可编程逻辑器件XC9572XL使用JTAG引脚(TCK、TDI、TDO、TMS、VREF、GND)用于与器件进行调试和编程通信。更详细的内容可以阅读1149.1-2013 - IEEE测试接入端口和边界扫描架构标准

| 信号名称 | 要求 | 描述 |

|---|---|---|

| Test Clock Input (TCK) | 必须 | 提供基本的时钟信号,驱动整个 TAP 操作。 |

| Test Mode Selection (TMS) | 必须 | 控制 TAP 状态机的状态转换,有效沿是在 TCK 的上升沿。 |

| Test Data Input (TDI) | 必须 | 串行输入数据到目标设备的特定寄存器,由 TCK 驱动。 |

| Test Data Output (TDO) | 必须 | 串行输出从目标设备特定寄存器中读取的数据,由 TCK 驱动。 |

| Voltage Reference (VREF) | 必须 | 电平参考电压,确定 JTAG 接口使用的逻辑电平,通常连接到供电电压。 |

| Test Reset (TRST) | 可选项 | 用于初始化 TAP 控制器的复位信号,非强制要求。 |

| Return Test Clock (RTCK) | 可选项 | 目标设备反馈给仿真器的时钟信号,用于同步 TCK 信号产生,如果未使用则直接接地。 |

| System Reset (nSRST) | 可选项 | 连接到目标板上的系统复位信号,可以复位目标系统,并可用于检测目标系统复位状态。 |

| User Input (USER IN) | 可选项 | 用户自定义输入接口,用于接收来自上位机的控制信号。 |

| User Output (USER OUT) | 可选项 | 用户自定义输出接口,用于向上位机反馈状态信息。 |

下载器驱动安装

- FT2232作为JTAG烧录器的使用步骤详解

- 驱动安装与使用指南

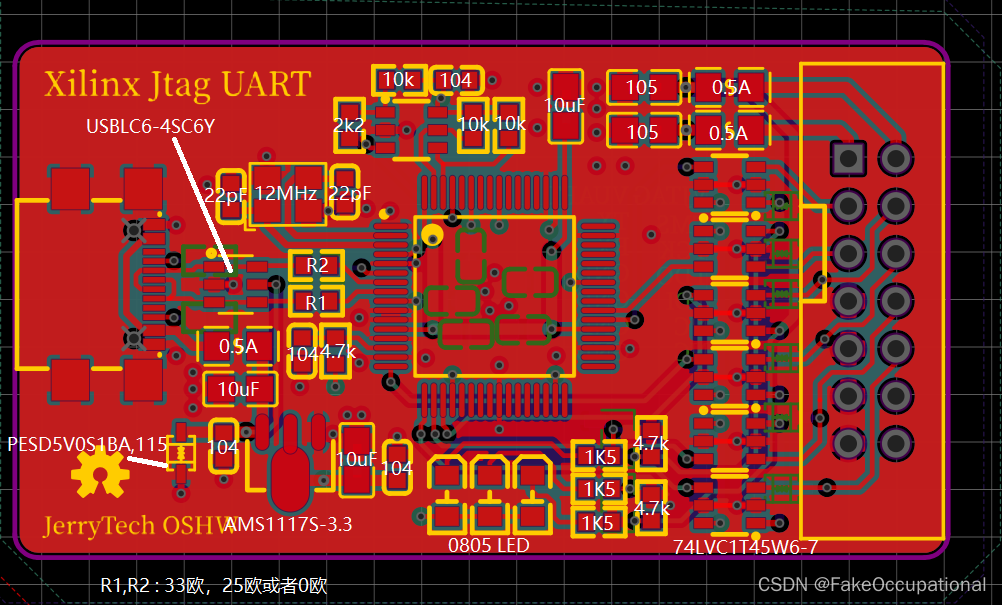

硬件开源项目

- 硬件源码:支持串口的高速Xilinx下载器,支持ISE,按教程刷eeprom

- https://oshwhub.com/cqzww/ft2232h-jtag,设计一款多功能JTAG调试器

- FT2232HL-jtag-clone

下载器硬件说明

USB to JTAG协议转换芯片FT2232----核心

| – | ||

|---|---|---|

| FT2232HL | FT2232H是FTDI的第5代USB设备芯片。 FT2232H是一个USB2.0高速(每秒480兆位)至UART/FIFO 芯片。 具有在多种工业标准串行或并行接口配置的能力。 | |

| 93LC56BT-I/OT | EEPROM(Electrically Erasable Programmable Read-Only Memory,电可擦可编程只读存储器) | FT2232外挂的EEPROM使用推荐的93LC56B(容量为2KB),实际配置文件大小在1KB~2KB之间。 |

| TAXM27.12M4RLBCCT2T | 无源晶振 |

电平转换芯片(比如74LVC1T45)---- 输出

- 比如一个电路用TTL 逻辑电平标准(通常为高电平3.3V以上,低电平0.8V以下),而另一个电路使用 CMOS 逻辑电平标准(通常为高电平约3.3V,低电平约0V),74LVC1T45可以实现单向转换

- 74LVC1T45的技术资料

- 注:因为LDO的输出是不变的,所以不能转换逻辑

CG

-

电子学姐手把手教你做赛灵思FPGA下载器

-

FT2232HL制作JTAG下载器驱动安装教程

-

Xilinx Platform Cable USB II 下载器驱动安装教程——Win10

-

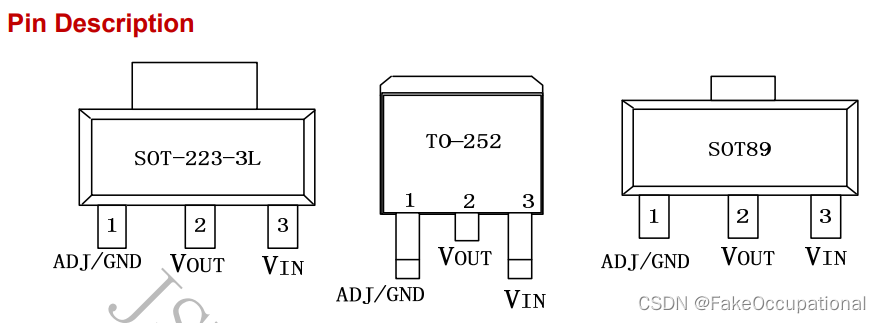

硬件踩坑记录:AMS1117S-3.3买错封装了,应该是SOT89封装的,买的SOT-223-3L。

-

晶振焊接不存在方向性

-

ESD有单向(A)和双向(C)之分,ESD5V0S1BA是双向的,焊接时不需要区分正负极性

-

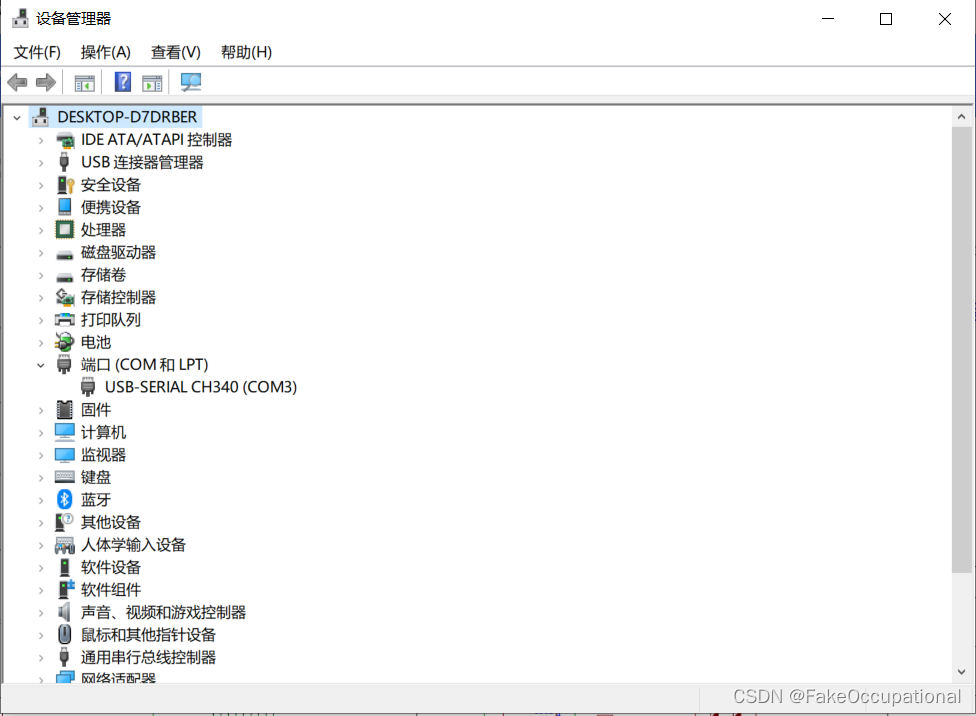

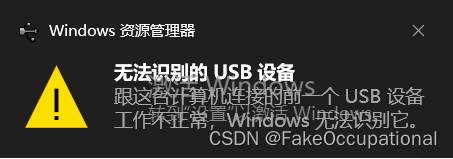

打开我的设备管理器,插入CH340会有端口出现,但是我焊接的板子插入没有任何显示。插那个fdti的jtag下载器应该会有一个usb c,两个com 7和com 8的接口显示

-

一开始插上没有任何显示,用风枪吹了一下,显示以下结果:

-

还有显示有关 dual r232 hs的提示

-

然后我换了一个晶振还是又变为没有任何显示了,是FT2232的问题还是晶振的问题啊?

-

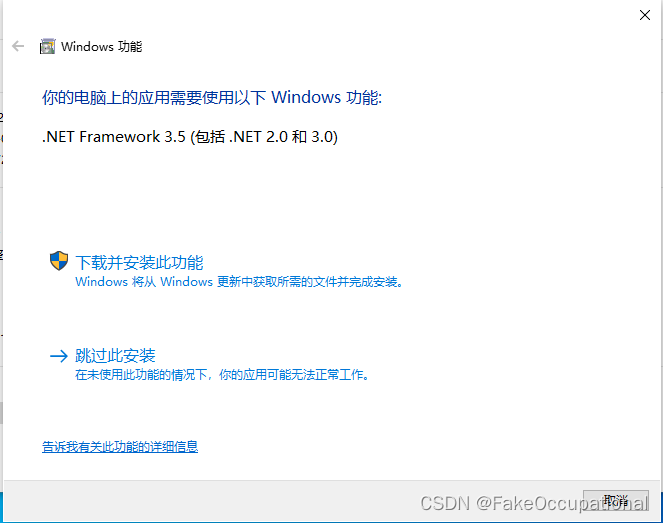

DigilentFTDIConfig安装也没办法用(也是因为没办法识别硬件)

)

| 服务端请求伪造 SSRF)

2024.6.24~2024.6.30)

)

)